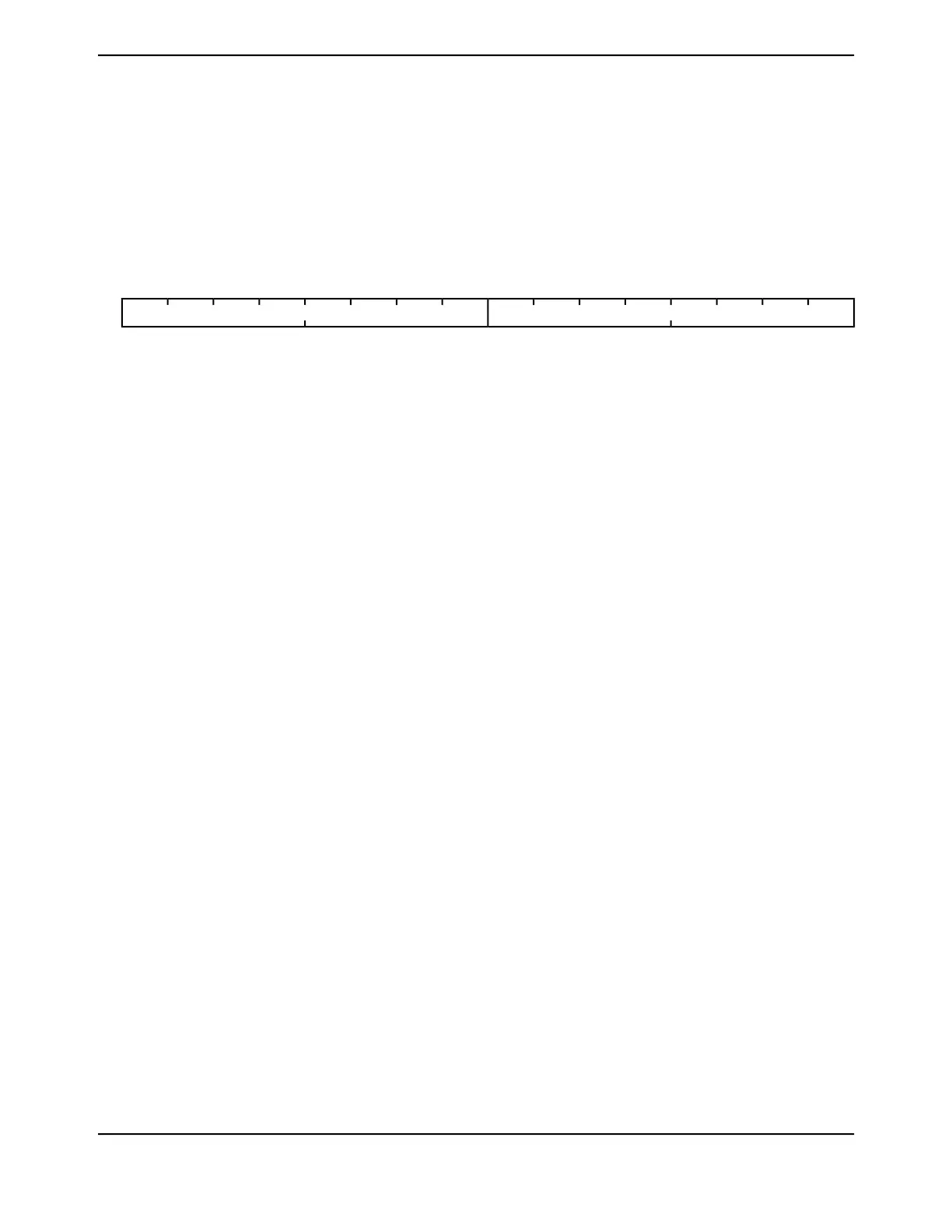

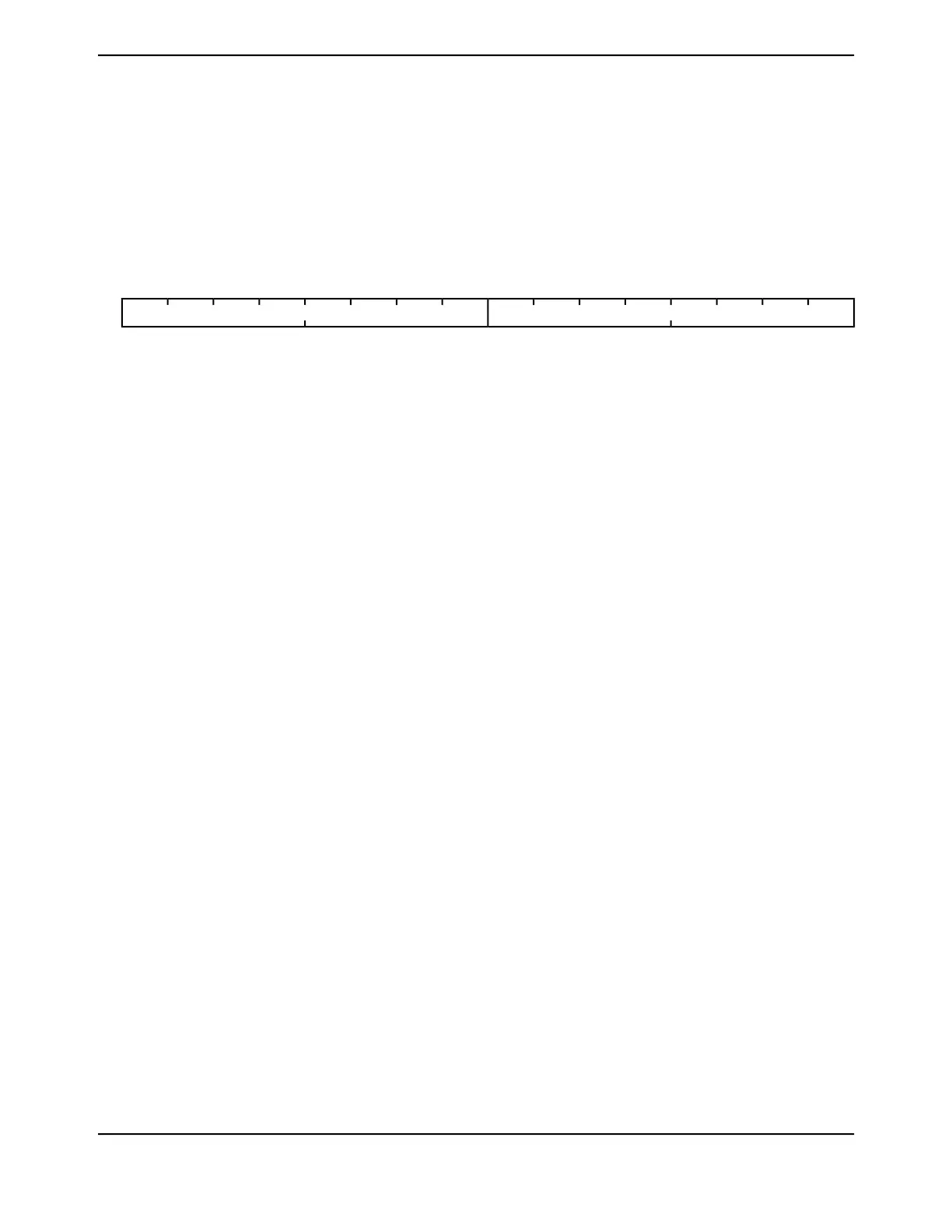

Register 96: Ethernet PHY BIST Control and Status 1 - MR27 (EPHYBICSR1),

address 0x01B

This register provides the total number of error bytes that are received by the PRBS checker and

defines the Inter-Packet Gap (IPG) for the packet generator.

Ethernet PHY BIST Control and Status 1 - MR27 (EPHYBICSR1)

Base n/a

Address 0x01B

Type RW, reset 0x007D

0123456789101112131415

IPGLENGTHERRCNT

RWRWRWRWRWRWRWRWROROROROROROROROType

1011111000000000Reset

DescriptionResetTypeNameBit/Field

BIST Error Count

This field holds the number of erroneous bytes that were received by

the PRBS checker. The value in this register is locked when a write is

done to bit 15.

When the PRBSM field in the EPHYBISCR register (0x0016) is set to

zero, the count stops at 0xFF. See the EPHYBISCR register for further

details.

0x00ROERRCNT15:8

BIST IPG Length

Inter Packet Gap (IPG) Length defines the size of the gap (in bytes)

between any 2 successive packets generated by the BIST. Default value

is 0x7D, which is equal to 125 bytes.

0x7DRWIPGLENGTH7:0

June 18, 20141638

Texas Instruments-Production Data

Ethernet Controller

Loading...

Loading...