Register 76: Ethernet PHY Auto-Negotiation Advertisement - MR4 (EPHYANA),

address 0x004

This register contains the advertised abilities of this device as they are transmitted to its link partner

during Auto-Negotiation.

Ethernet PHY Auto-Negotiation Advertisement - MR4 (EPHYANA)

Base n/a

Address 0x004

Type RW, reset 0x01E1

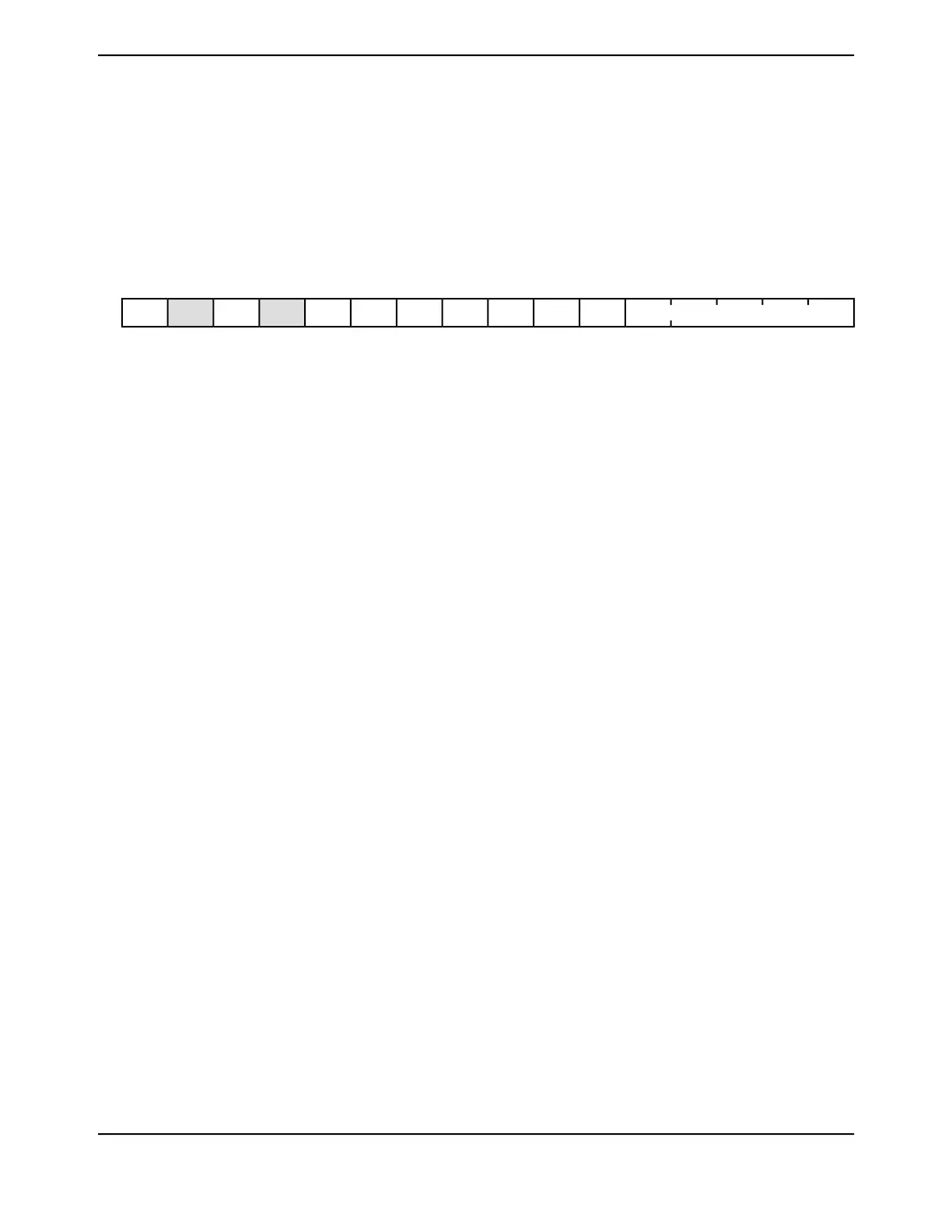

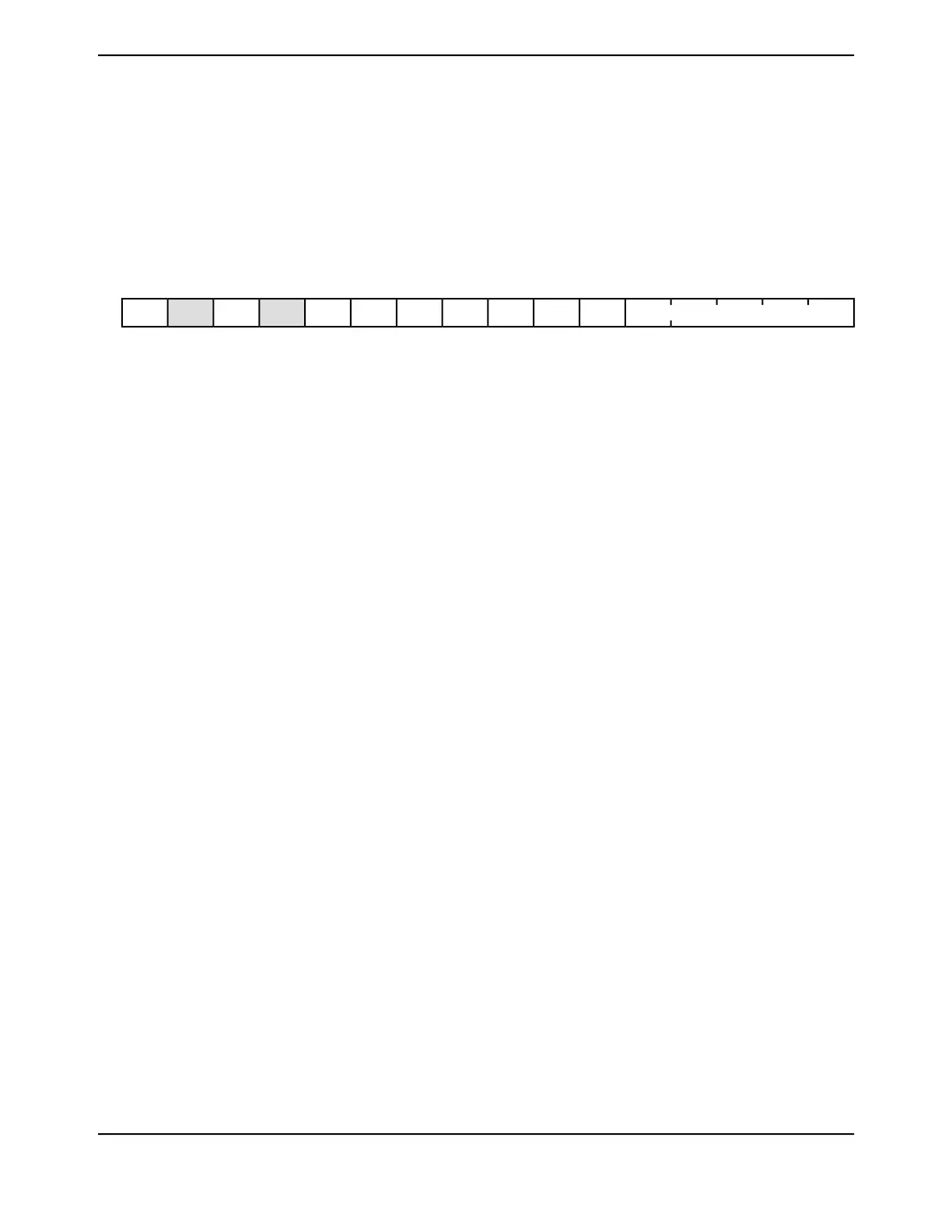

0123456789101112131415

SELECT10BT10BTFD100BTX

100BTXFD

100BT4PAUSEASMDUPreservedRFreservedNP

RWRWRWRWRWRWRWRWRWRORWRWRORWRORWType

1000011110000000Reset

DescriptionResetTypeNameBit/Field

Next Page Indication

DescriptionValue

Next Page Transfer not desired.0

Next Page Transfer desired.1

0RWNP15

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0ROreserved14

Remote Fault

DescriptionValue

No Remote Fault detected.0

Advertises that this device has detected a Remote Fault.1

0RWRF13

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0ROreserved12

Asymmetric PAUSE support for Full Duplex Links

Encoding and resolution of PAUSE bits is defined in IEEE 802.3 Annex

28B, Tables 28B-2 and 28B-3, respectively. Pause resolution status is

reported in the Pause Status bits [13:12], of the Ethernet PHY Control

(EPHYCTL) register.

DescriptionValue

Asymmetric PAUSE not implemented.0

Asymmetric PAUSE implemented. Advertise that the MAC has

implemented both the optional MAC control sublayer and the

pause function as specified in clause 31 and annex 31B of

IEEE802.3u.

1

0RWASMDUP11

1597June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...