Register 15: Flash DMA Address Size (FLASHDMASZ), offset 0xFD0

The FLASHDMASZ register contains the area of Flash that the µDMA can access.

Note: The µDMA can access Flash in Run Mode only (not available in low power modes).

Flash DMA Address Size (FLASHDMASZ)

Base 0x400F.D000

Offset 0xFD0

Type RW, reset 0x0000.0000

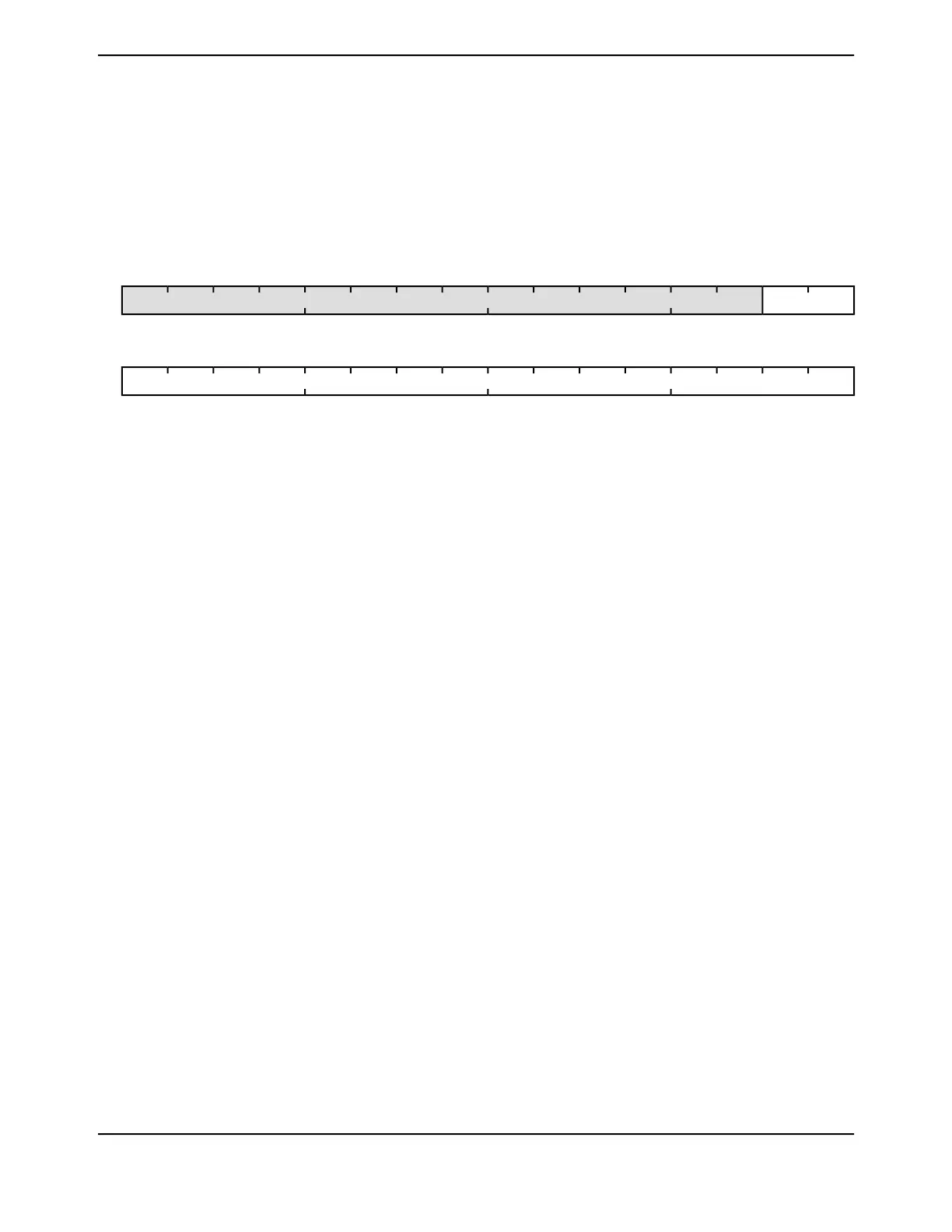

16171819202122232425262728293031

SIZEreserved

RWRWROROROROROROROROROROROROROROType

0000000000000000Reset

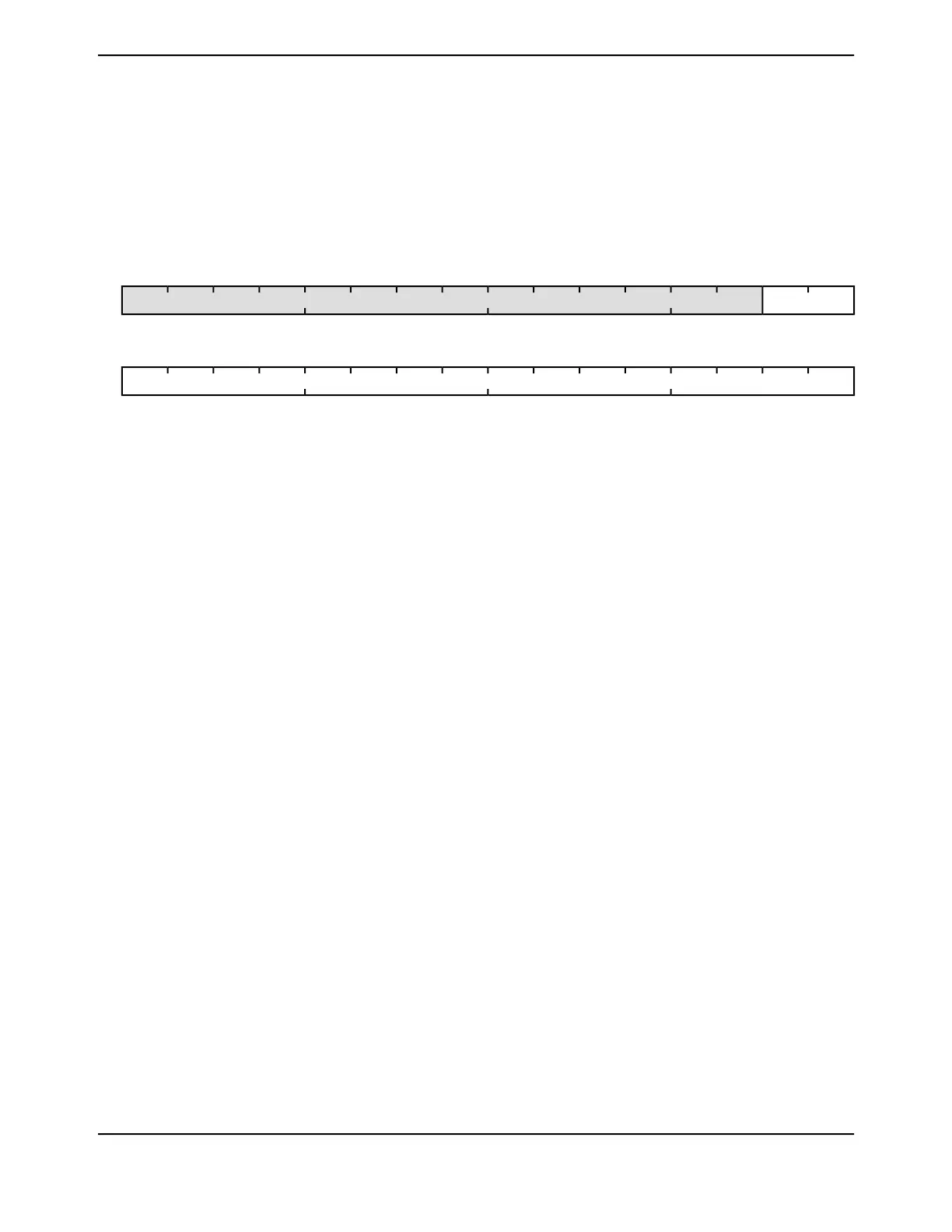

0123456789101112131415

SIZE

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWRWType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000ROreserved31:18

µDMA-accessible Memory Size

The size of the region addressable by the µDMA. Note that the DFA bit

must be set in the FLASHPP register before this value can be

programmed. Size of region is defined as 2*(SIZE + 1) KB.

0x0RWSIZE17:0

649June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...