Register 7: Watchdog Test (WDTTEST), offset 0x418

This register provides user-enabled stalling when the microcontroller asserts the CPU halt flag

during debug.

Watchdog Test (WDTTEST)

WDT0 base: 0x4000.0000

WDT1 base: 0x4000.1000

Offset 0x418

Type RW, reset 0x0000.0000

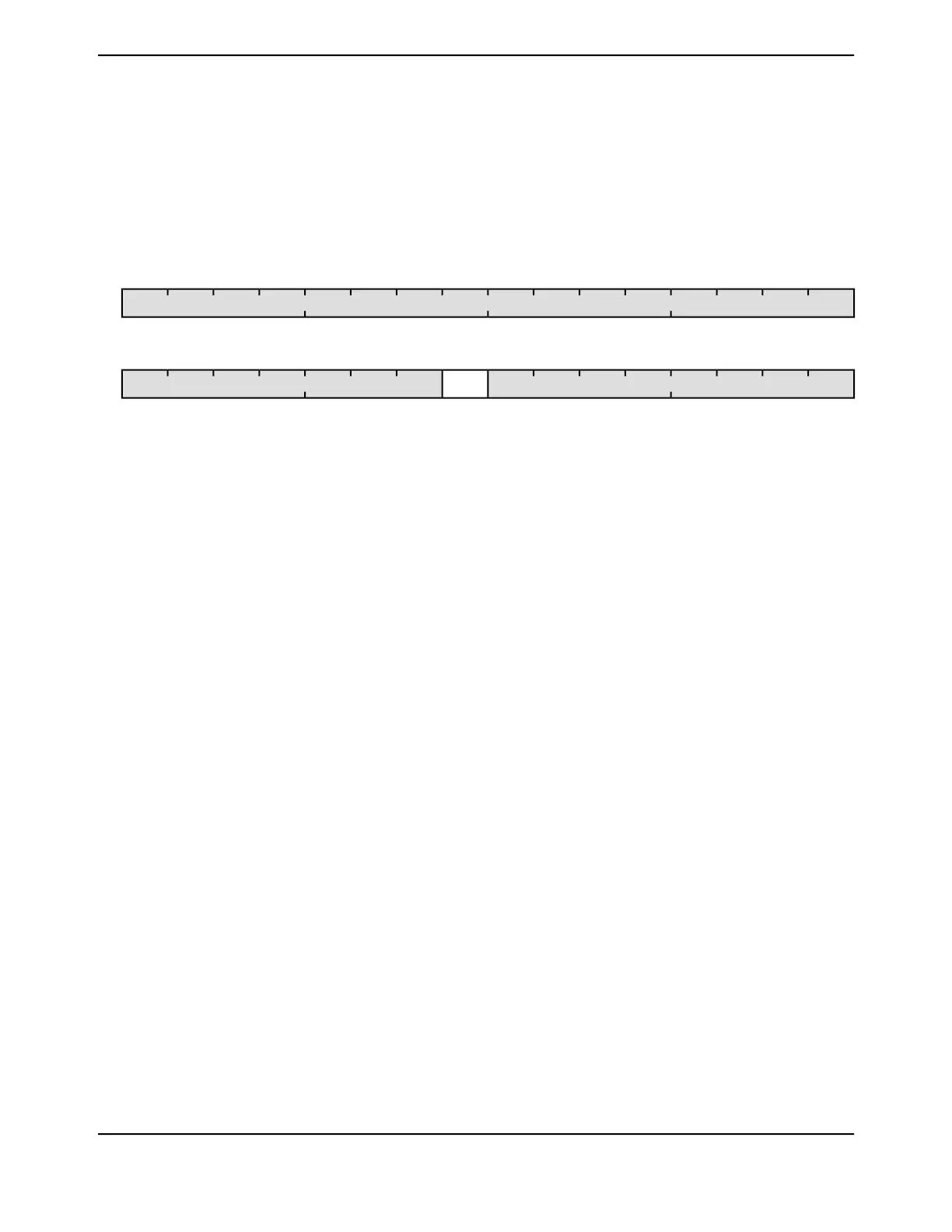

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

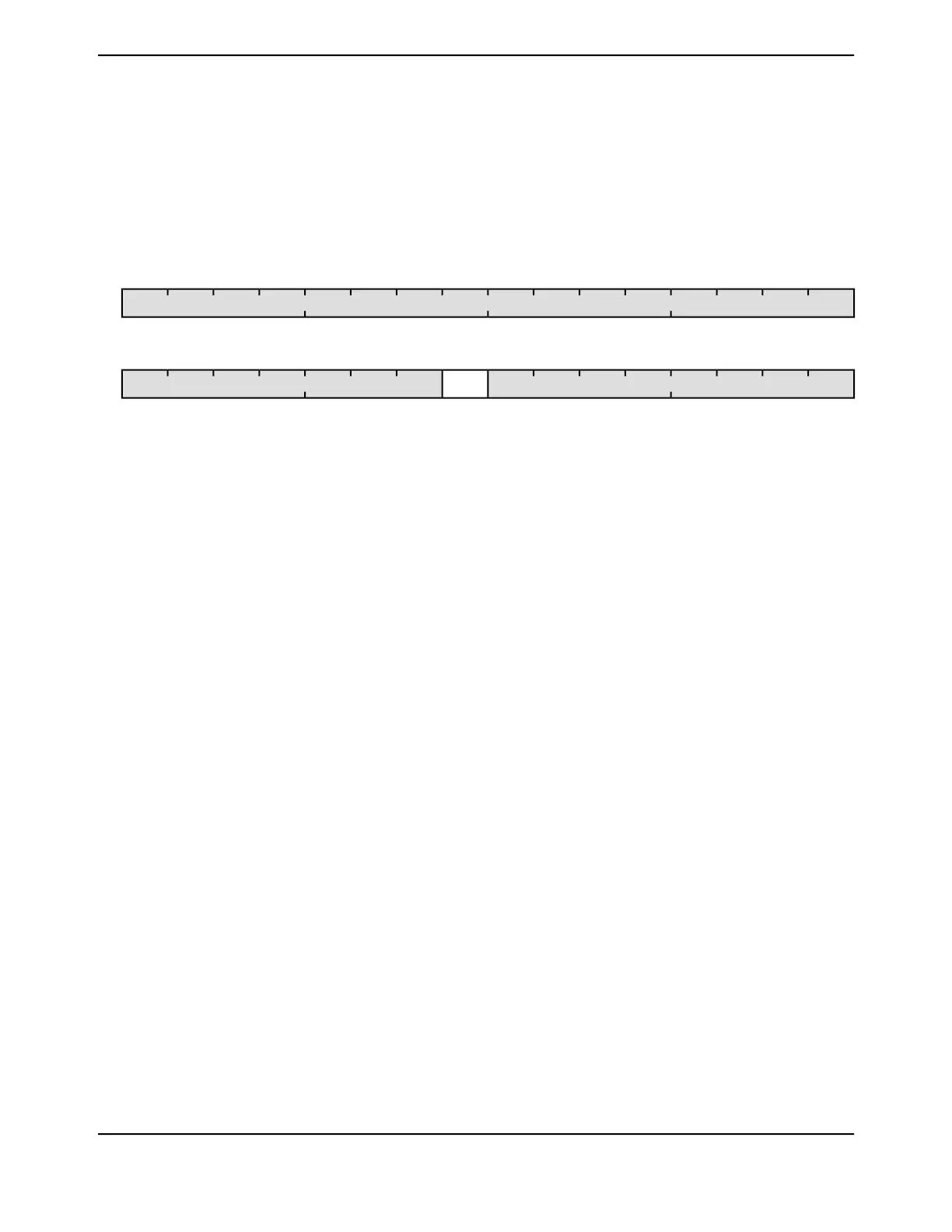

0123456789101112131415

reservedSTALLreserved

RORORORORORORORORWROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.00ROreserved31:9

Watchdog Stall Enable

DescriptionValue

The watchdog timer continues counting if the microcontroller is

stopped with a debugger.

0

If the microcontroller is stopped with a debugger, the watchdog

timer stops counting. Once the microcontroller is restarted, the

watchdog timer resumes counting.

1

0RWSTALL8

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x00ROreserved7:0

1039June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...