Register 13: Flash Configuration Register (FLASHCONF), offset 0xFC8

The FLASHCONF register allows the user to enable or disable various properties of the Flash. The

force bits, FBFON and FBFOFF, can be used to test code performance and execution by turning the

prefetch buffers on and subsequently forcing them off.

Flash Configuration Register (FLASHCONF)

Base 0x400F.D000

Offset 0xFC8

Type RW, reset 0x0000.0000

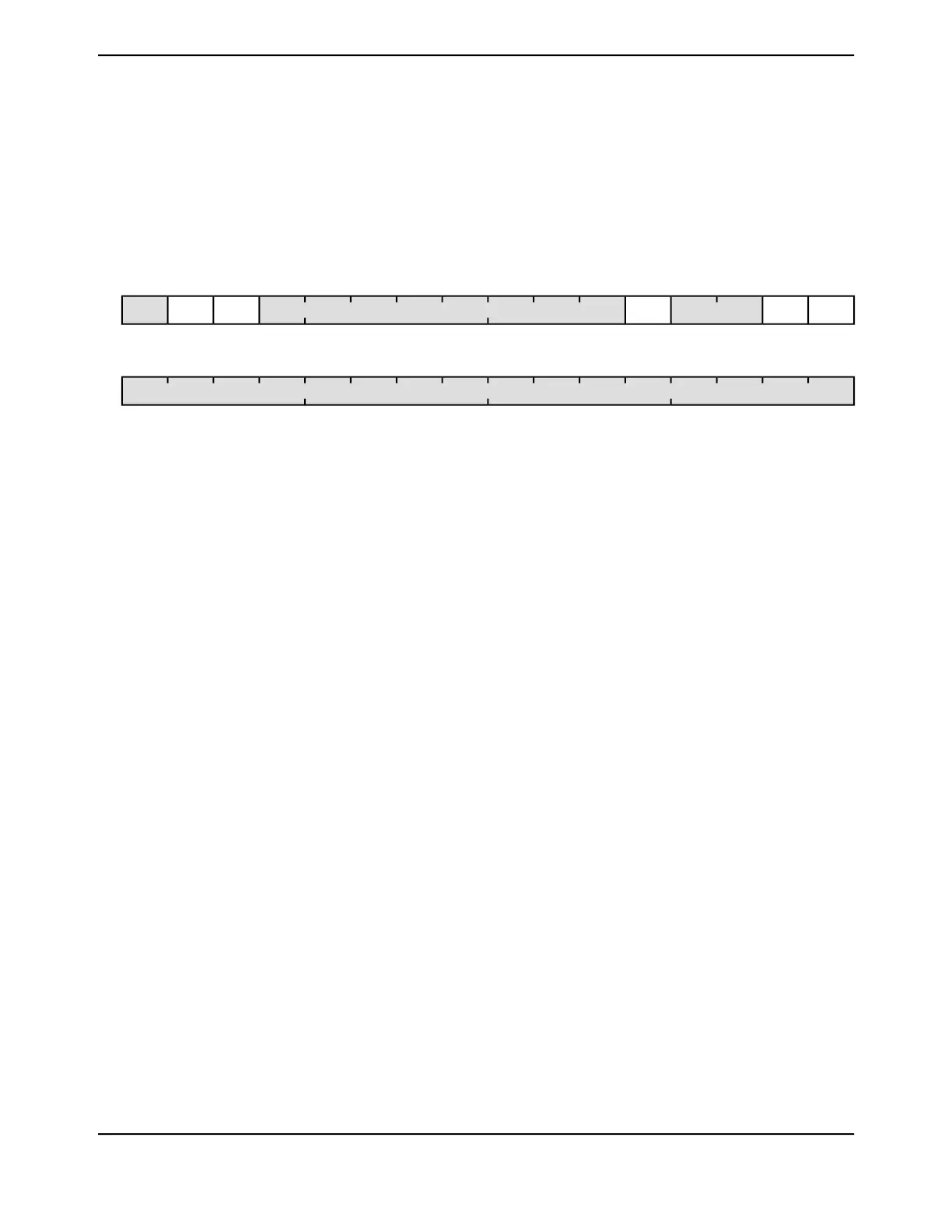

16171819202122232425262728293031

FPFOFFFPFONreservedCLRTVreservedSPFEFMMEreserved

RWRWRORORWRORORORORORORORORWRWROType

0000000000000000Reset

0123456789101112131415

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0ROreserved31

Flash Mirror Mode Enable

DescriptionValue

Flash mirror mode is disabled.0

Flash mirror mode feature is enabled. Access to the lower banks

is translated to upper.

1

0x0RWFMME30

Single Prefetch Mode Enable

DescriptionValue

A 4x256-bit prefetch buffer is enabled and used.0

A single 2x256-bit prefetch buffer is enabled and used.1

0x0RWSPFE29

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x000ROreserved28:21

Clear Valid Tags

This is a self-clearing bit.

DescriptionValue

No effect.0

Clear valid tags in the prefetch buffer.1

0RWCLRTV20

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0ROreserved19:18

645June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...