27.10 Sleep Modes

The following tables can be used to calculate the maximum wake time from Sleep or Deep Sleep

depending on the specific application. Depending on the application configuration, each of the

parameters, except for T

FLASH

, add sequential latency to the wake time. Flash restoration happens

in parallel to the other wake processes and its wake time is normally absorbed by the other latencies.

As an example, the wake time for a device in Deep Sleep, with the PIOSC and PLL turned off and

the Flash and SRAM in low power mode is calculated as follows:

Wake Time = T

PIOSCDS

+ T

PLLDS

+ T

SRAMLPDS

T

FLASH

does not contribute to this equation since all other parameters are greater in value.

Note that in Sleep mode the wake time due to a clock source is zero because the device uses the

same clock configuration in Run mode; thus, there is no latency involved with respect to the clocks.

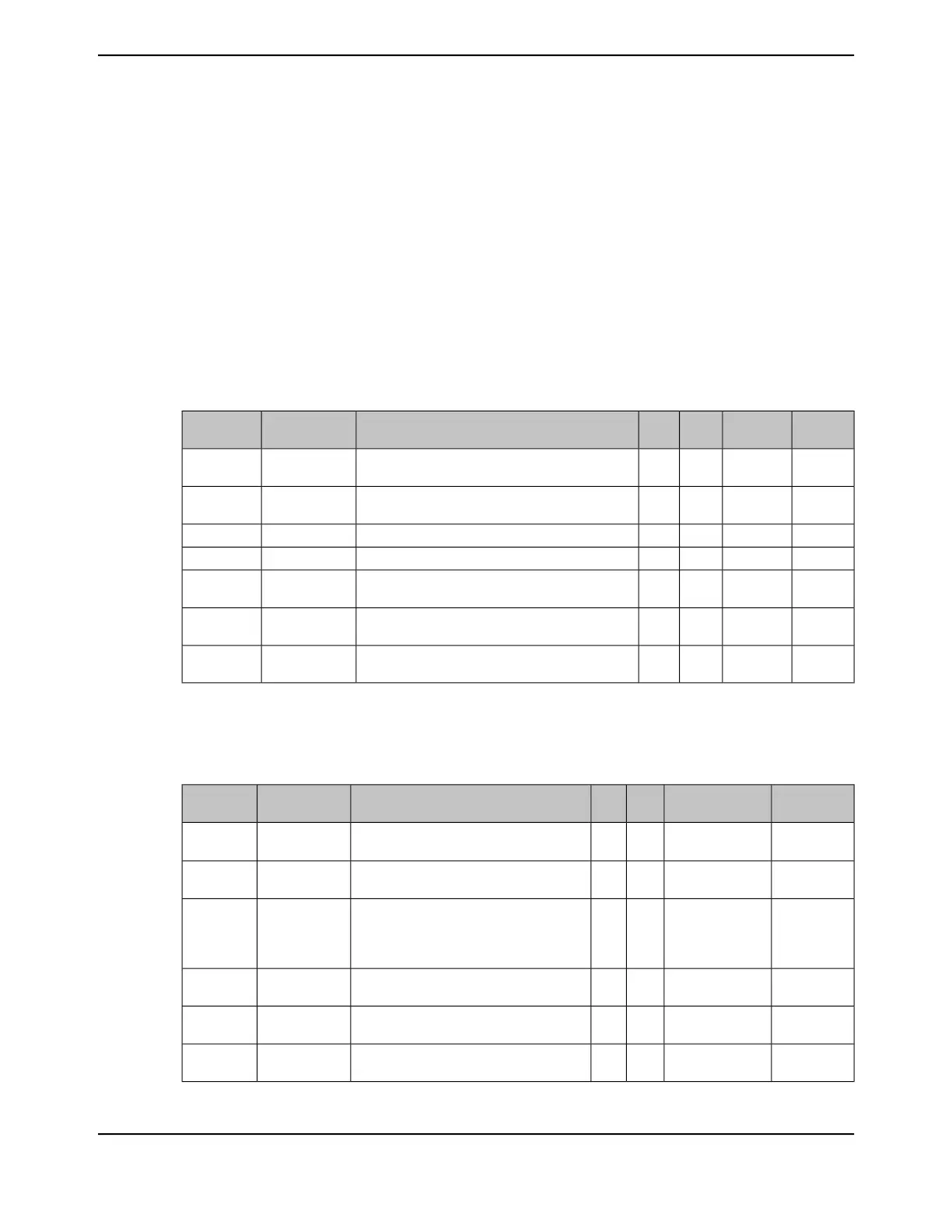

Table 27-27. Wake from Sleep Characteristics

UnitMaxNomMinParameter NameParameterParameter

No

µsN/A

a

--Time to restore PIOSC as System Clock in Sleep

mode

T

PIOSC

D1

µsN/A

b

--Time to restore MOSC as System Clock in Sleep

mode

T

MOSC

D2

µsN/A

c

--Time to restore PLL as System Clock in Sleep modeT

PLL

D3

µs39--Time to restore LDO to 1.2 V in Sleep modeT

LDO

D4

µs5--Time to restore Flash to active state from low power

state in Sleep mode

T

FLASH

D5

µs15--Time to restore SRAM to active state from low

power state in Sleep mode

T

SRAMLP

D6

µs15--Time to restore SRAM to active state from standby

state in Sleep mode

T

SRAMSTBY

D7

a. Because the PIOSC is enabled in both Run and Sleep Mode for this configuration, no restoration time is required.

b. Because the MOSC is enabled in both Run and Sleep Mode for this configuration, no restoration time is required.

c. Because the PLL is enabled in both Run and Sleep Mode for this configuration, no restoration time is required.

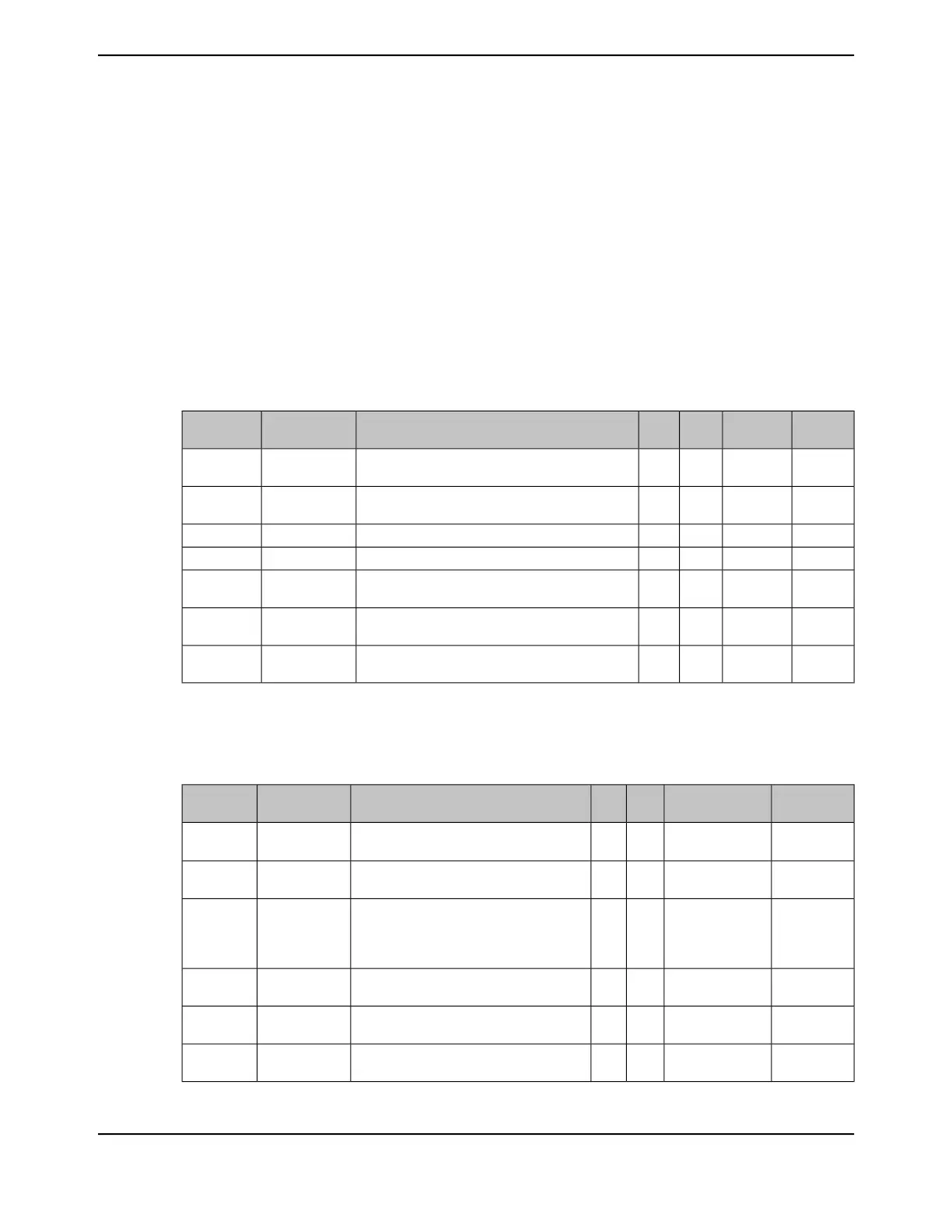

Table 27-28. Wake from Deep Sleep Characteristics

UnitMaxNomMinParameter NameParameterParameter

No

Deep Sleep

Clock Cycles

a

14--Time to restore PIOSC as System Clock in

Deep Sleep Mode

T

PIOSCDS

D8

ms18--Time to restore MOSC as System Clock in

Deep Sleep Mode

T

MOSCDS

D9

clocks1 cycle of Deep

Sleep Clock + 512

cycles of PLL

reference Clock

a

--Time to restore PLL as System Clock in

Deep Sleep Mode

T

PLLDS

D10

µs39--Time to restore LDO to 1.2 V in Deep Sleep

Mode

T

LDODS

D11

µs5--Time to restore Flash to active state from

low power state

T

FLASHLPDS

D12

µs15--Time to restore SRAM to active state from

low power state

T

SRAMLPDS

D13

1843June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...