Register 7: EPI General-Purpose Configuration (EPIGPCFG), offset 0x010

Important: The MODE field in the EPICFG register determines which configuration register is

accessed for offsets 0x010 and 0x014.

To access EPIGPCFG, the MODE field must be 0x0.

The General-Purpose configuration register is used to configure the control, data, and address pins.

This mode can be used for custom interfaces with FPGAs, CPLDs, and for digital data acquisition

and actuator control. Note that this register is reset when the MODE field in the EPICFG register is

changed. If another mode is selected and the General-purpose mode is selected again, the register

the values must be reinitialized.

This mode is designed for 3 general types of use:

■ Extremely high-speed clocked interfaces to FPGAs and CPLDs, with 3 sizes of data and optional

address. Framing and clock-enable permit more optimized interfaces.

■ General parallel GPIO. From 1 to 32 pins may be written or read, with the speed precisely

controlled by the baud rate in the EPIBAUD register (when used with the NBRFIFO and/or the

WFIFO) or by rate of accesses from software or μDMA.

■ General custom interfaces of any speed.

The configuration allows for choice of an output clock (free running or gated), a framing signal (with

frame size), a ready input (to stretch transactions), read and write strobes, address of varying sizes,

and data of varying sizes. Additionally, provisions are made for splitting address and data phases

on the external interface.

EPI General-Purpose Configuration (EPIGPCFG)

Base 0x400D.0000

Offset 0x010

Type RW, reset 0x0000.0000

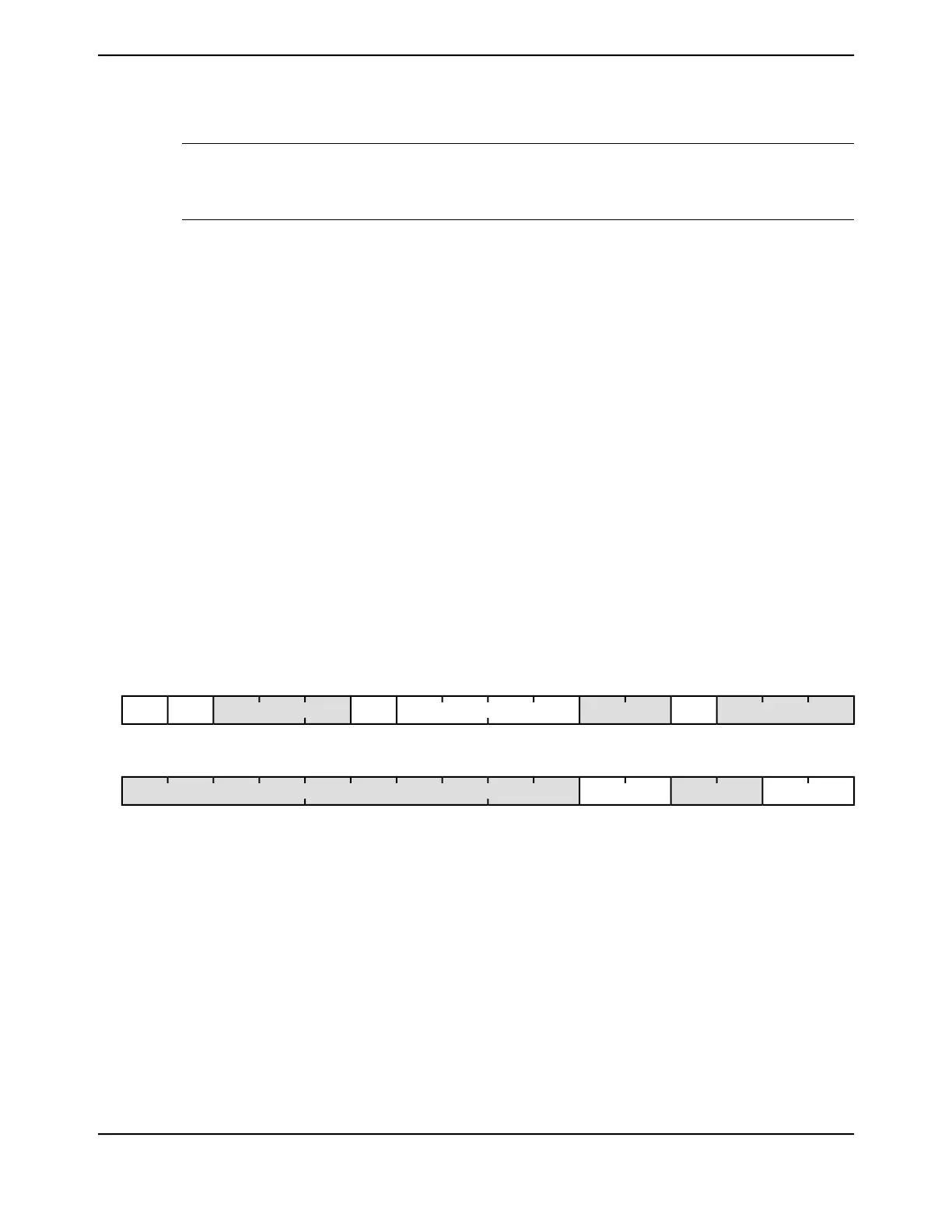

16171819202122232425262728293031

reservedWR2CYCreservedFRMCNTFRM50reservedCLKGATECLKPIN

RORORORWRORORWRWRWRWRWRORORORWRWType

0000000000000000Reset

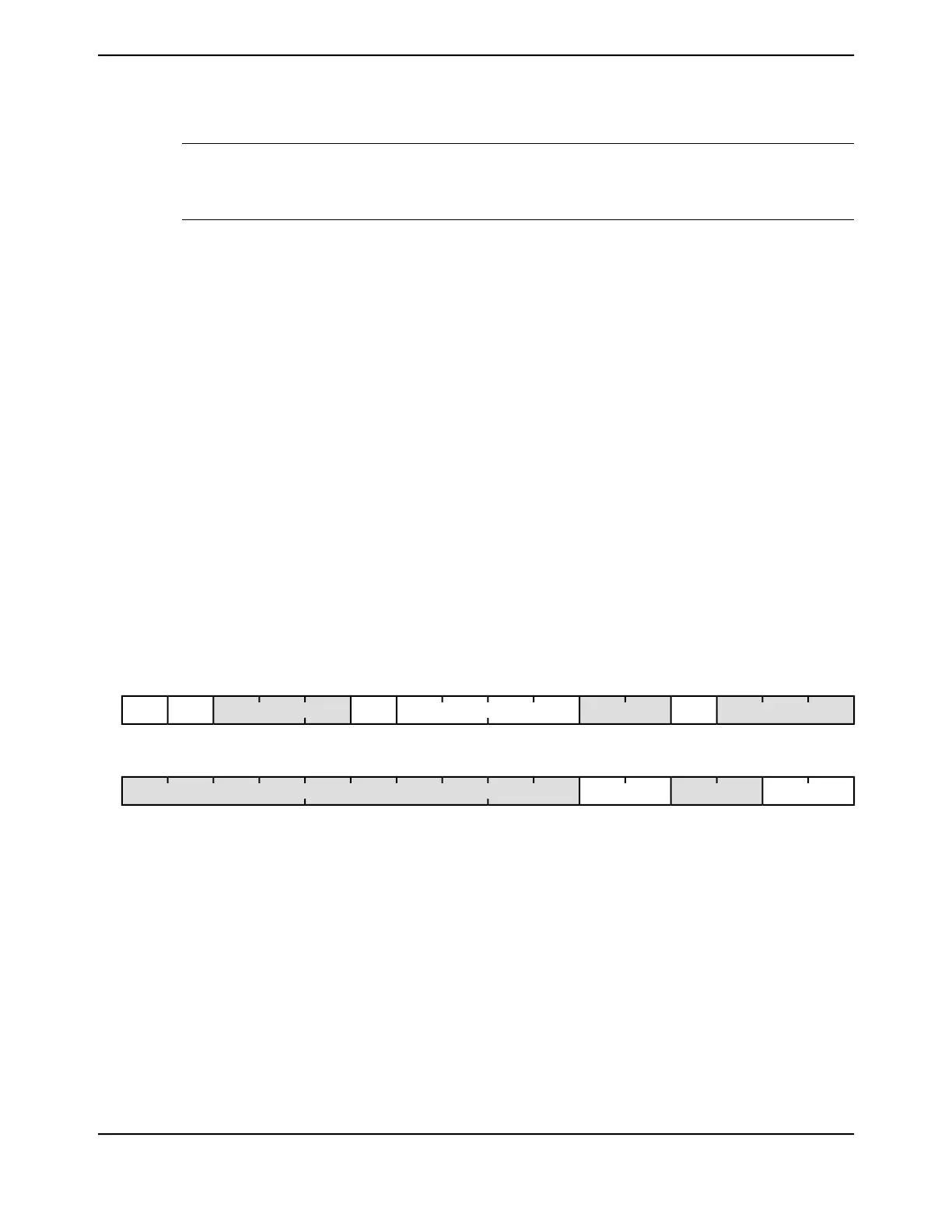

0123456789101112131415

DSIZEreservedASIZEreserved

RWRWRORORWRWROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Clock Pin

DescriptionValue

No clock output.0

EPI0S31 functions as the EPI clock output.1

The EPI clock is generated from the COUNT0 field in the EPIBAUD

register (as is the system clock which is divided down from it).

0RWCLKPIN31

June 18, 2014876

Texas Instruments-Production Data

External Peripheral Interface (EPI)

Loading...

Loading...