Register 2: UART Receive Status/Error Clear (UARTRSR/UARTECR), offset

0x004

The UARTRSR/UARTECR register is the receive status register/error clear register.

In addition to the UARTDR register, receive status can also be read from the UARTRSR register.

If the status is read from this register, then the status information corresponds to the entry read from

UARTDR prior to reading UARTRSR. The status information for overrun is set immediately when

an overrun condition occurs.

The UARTRSR register cannot be written.

A write of any value to the UARTECR register clears the framing, parity, break, and overrun errors.

All the bits are cleared on reset.

Read-Only Status Register

UART Receive Status/Error Clear (UARTRSR/UARTECR)

UART0 base: 0x4000.C000

UART1 base: 0x4000.D000

UART2 base: 0x4000.E000

UART3 base: 0x4000.F000

UART4 base: 0x4001.0000

UART5 base: 0x4001.1000

UART6 base: 0x4001.2000

UART7 base: 0x4001.3000

Offset 0x004

Type RO, reset 0x0000.0000

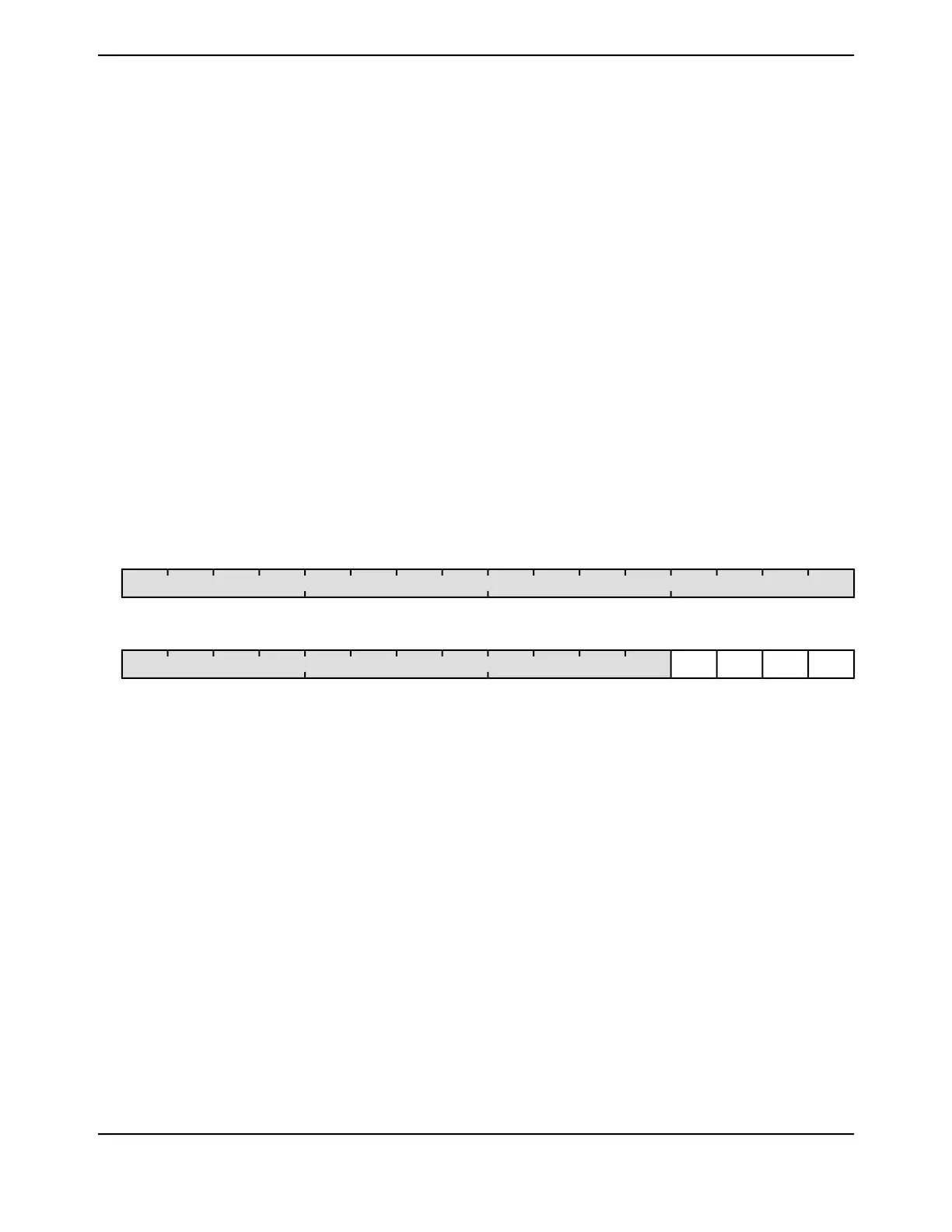

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

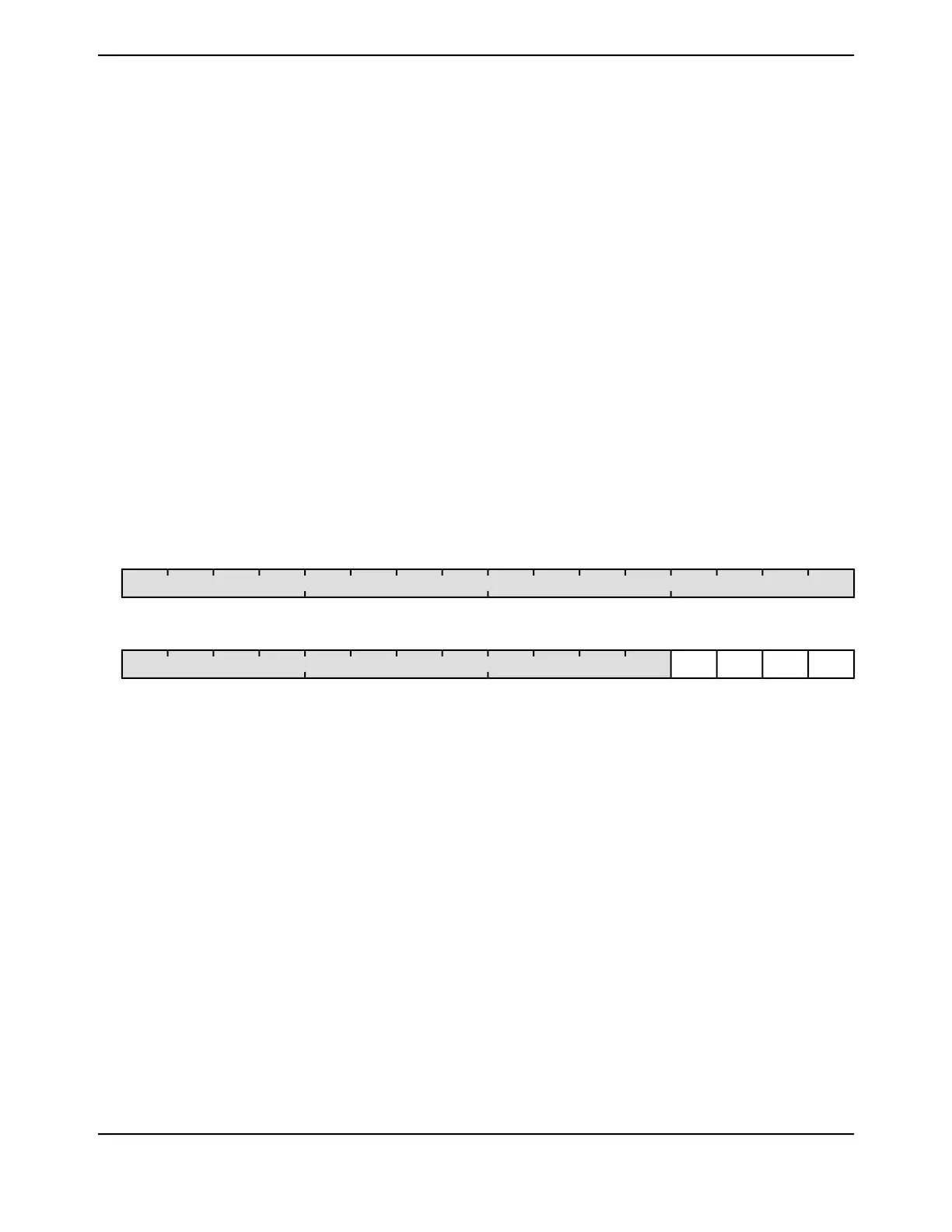

0123456789101112131415

FEPEBEOEreserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.000ROreserved31:4

UART Overrun Error

DescriptionValue

No data has been lost due to a FIFO overrun.0

New data was received when the FIFO was full, resulting in

data loss.

1

This bit is cleared by a write to UARTECR.

The FIFO contents remain valid because no further data is written when

the FIFO is full, only the contents of the shift register are overwritten.

The CPU must read the data in order to empty the FIFO.

0ROOE3

1177June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...