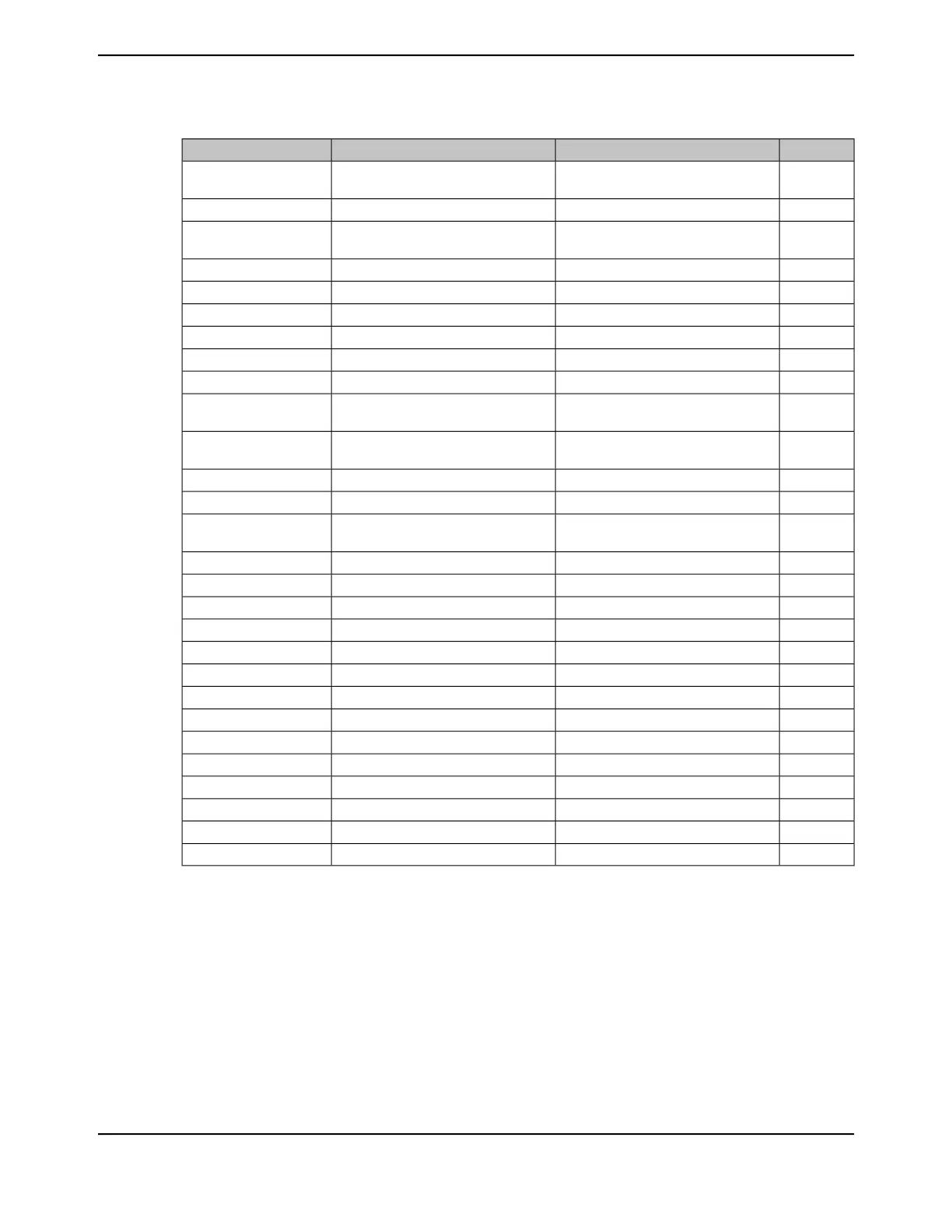

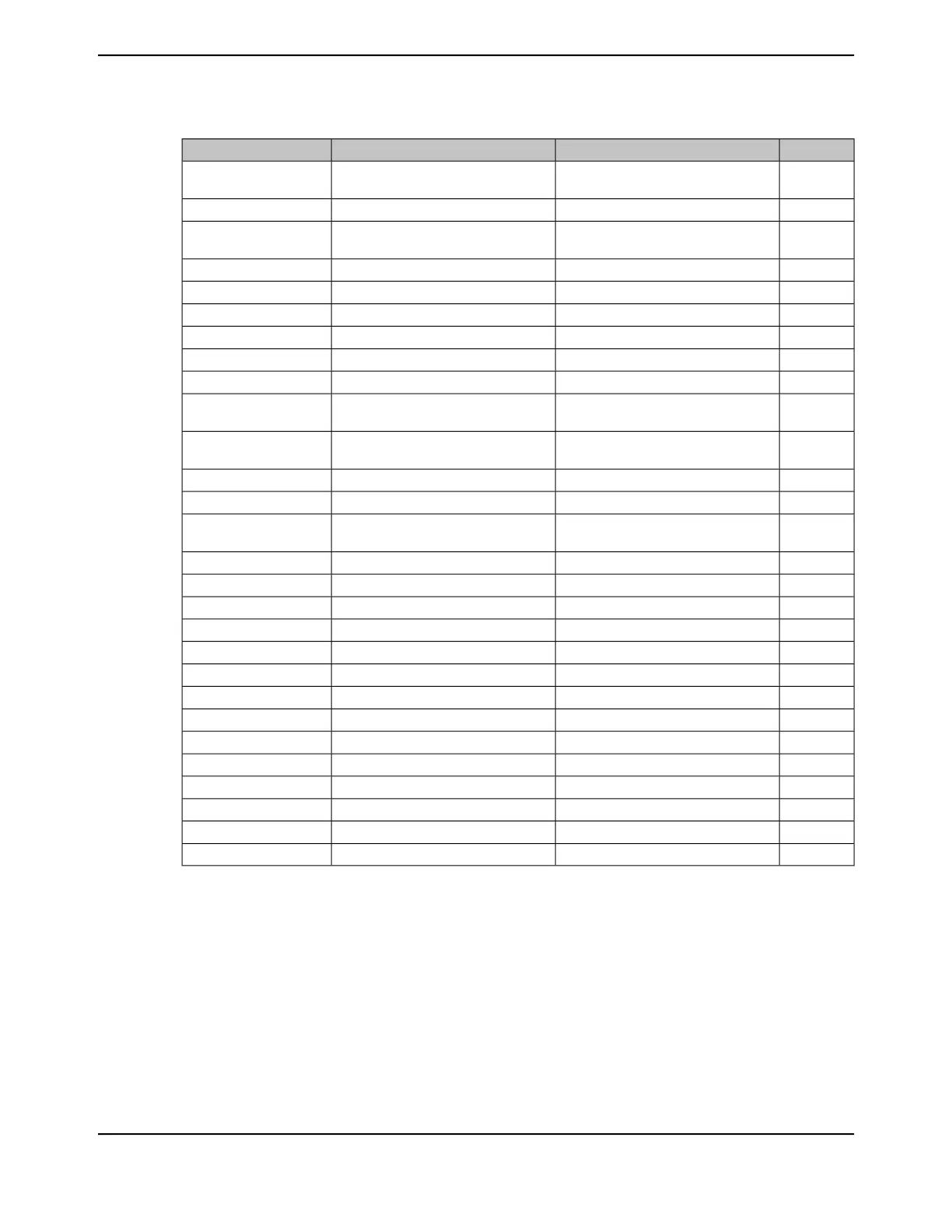

Table 2-13. Cortex-M4F Instruction Summary (continued)

FlagsBrief DescriptionOperandsMnemonic

-Floating-point Fused Negate Multiply

Accumulate

{Sd,} Sn, SmVFNMA.F32

-Floating-point Fused Multiply Subtract{Sd,} Sn, SmVFMS.F32

-Floating-point Fused Negate Multiply

Subtract

{Sd,} Sn, SmVFNMS.F32

-Load Multiple extension registersRn{!}, listVLDM.F<32|64>

-Load an extension register from memory<Dd|Sd>, [Rn]VLDR.F<32|64>

-Floating-point Multiply Accumulate{Sd,} Sn, SmVLMA.F32

-Floating-point Multiply Subtract{Sd,} Sn, SmVLMS.F32

-Floating-point Move immediateSd, #immVMOV.F32

-Floating-point Move registerSd, SmVMOV

-Copy ARM core register to single

precision

Sn, RtVMOV

-Copy 2 ARM core registers to 2 single

precision

Sm, Sm1, Rt, Rt2VMOV

-Copy ARM core register to scalarDd[x], RtVMOV

-Copy scalar to ARM core registerRt, Dn[x]VMOV

N,Z,C,VMove FPSCR to ARM core register or

APSR

Rt, FPSCRVMRS

FPSCRMove to FPSCR from ARM Core registerFPSCR, RtVMSR

-Floating-point Multiply{Sd,} Sn, SmVMUL.F32

-Floating-point NegateSd, SmVNEG.F32

-Floating-point Multiply and Add{Sd,} Sn, SmVNMLA.F32

-Floating-point Multiply and Subtract{Sd,} Sn, SmVNMLS.F32

-Floating-point Multiply{Sd,} Sn, SmVNMUL

-Pop extension registerslistVPOP

-Push extension registerslistVPUSH

-Calculates floating-point Square RootSd, SmVSQRT.F32

-Floating-point register Store MultipleRn{!}, listVSTM

-Stores an extension register to memorySd, [Rn]VSTR.F3<32|64>

-Floating-point Subtract{Sd,} Sn, SmVSUB.F<32|64>

-Wait for event-WFE

-Wait for interrupt-WFI

133June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...