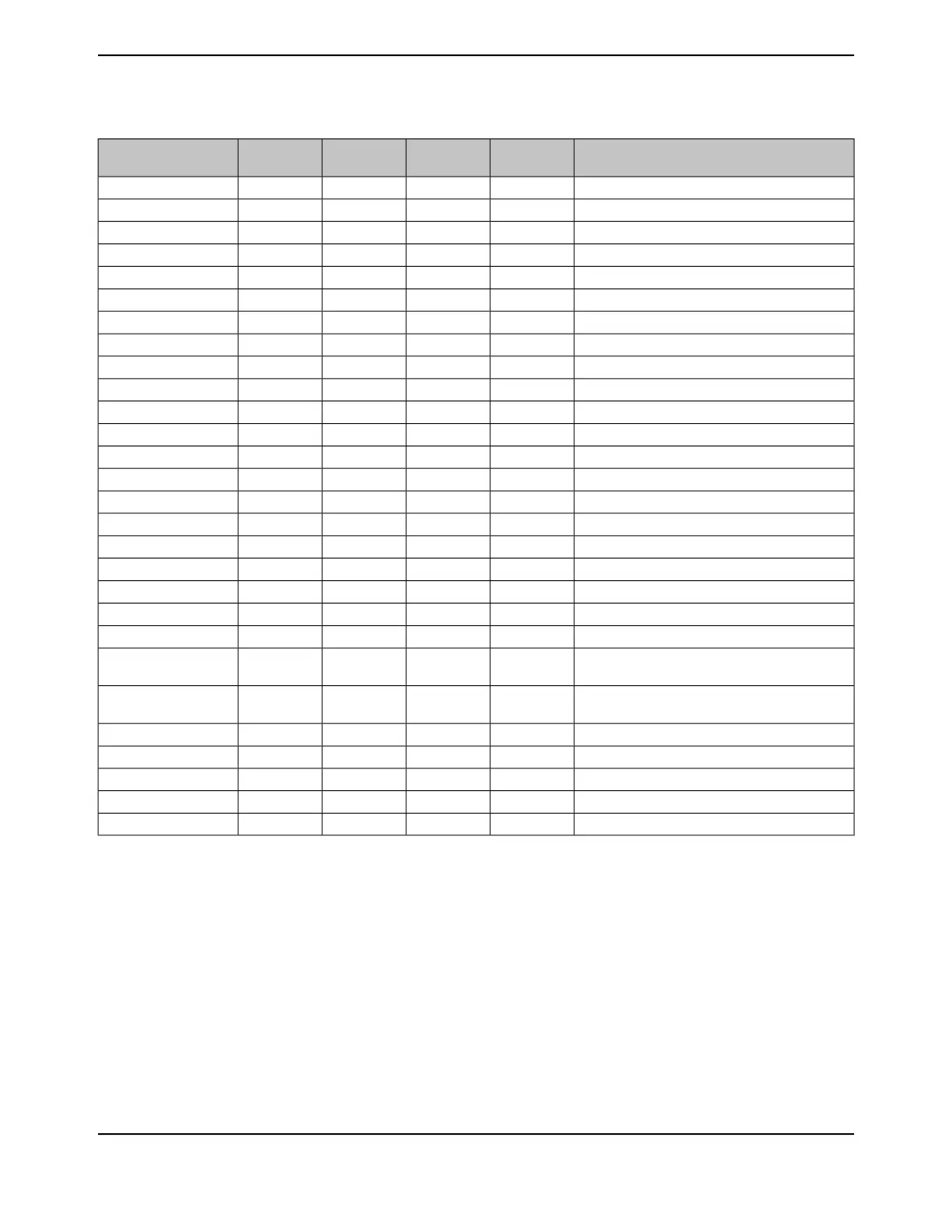

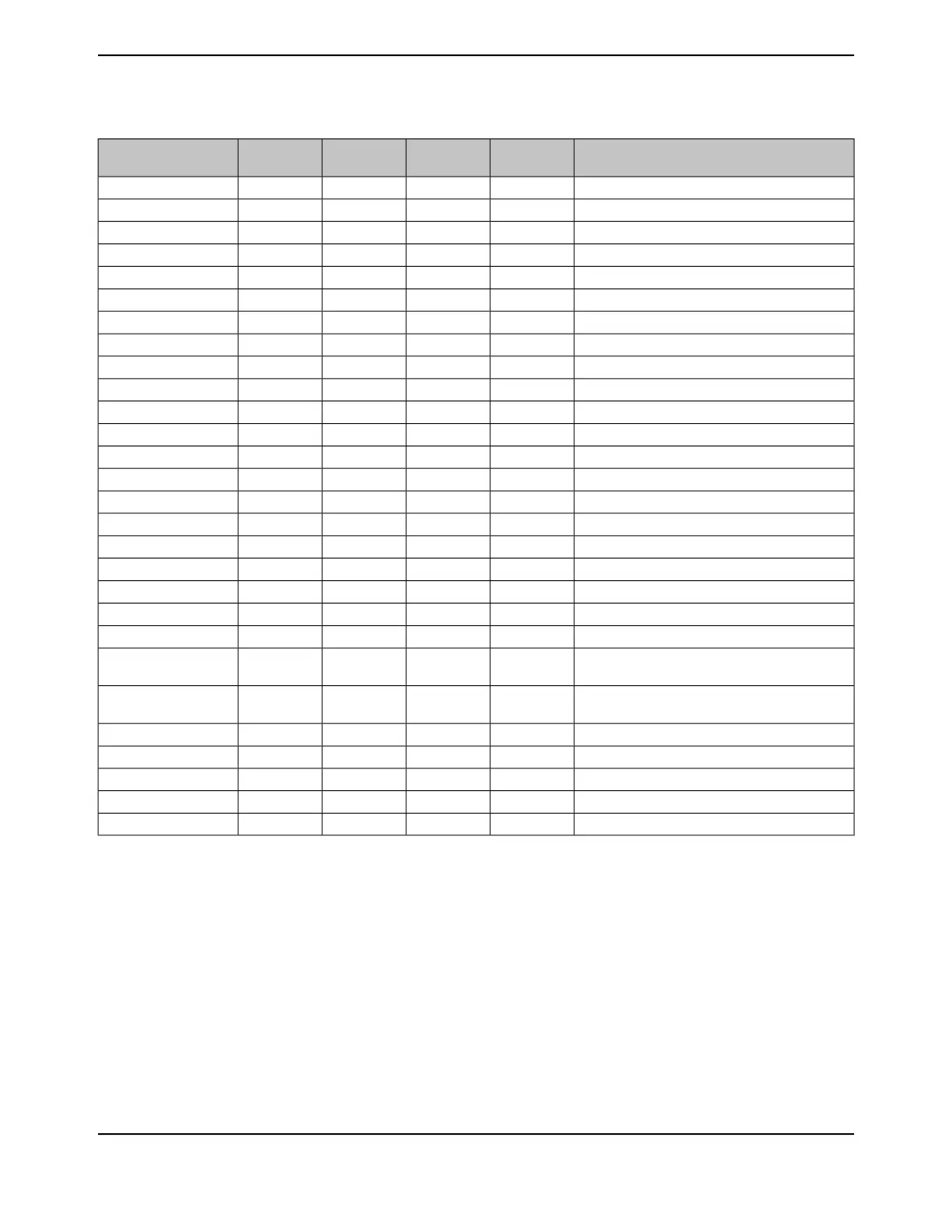

Table 11-1. External Peripheral Interface Signals (128TQFP) (continued)

DescriptionBuffer TypePin TypePin Mux / Pin

Assignment

Pin NumberPin Name

EPI module 0 signal 8.TTLI/OPA6 (15)40EPI0S8

EPI module 0 signal 9.TTLI/OPA7 (15)41EPI0S9

EPI module 0 signal 10.TTLI/OPG1 (15)50EPI0S10

EPI module 0 signal 11.TTLI/OPG0 (15)49EPI0S11

EPI module 0 signal 12.TTLI/OPM3 (15)75EPI0S12

EPI module 0 signal 13.TTLI/OPM2 (15)76EPI0S13

EPI module 0 signal 14.TTLI/OPM1 (15)77EPI0S14

EPI module 0 signal 15.TTLI/OPM0 (15)78EPI0S15

EPI module 0 signal 16.TTLI/OPL0 (15)81EPI0S16

EPI module 0 signal 17.TTLI/OPL1 (15)82EPI0S17

EPI module 0 signal 18.TTLI/OPL2 (15)83EPI0S18

EPI module 0 signal 19.TTLI/OPL3 (15)84EPI0S19

EPI module 0 signal 20.TTLI/OPQ0 (15)5EPI0S20

EPI module 0 signal 21.TTLI/OPQ1 (15)6EPI0S21

EPI module 0 signal 22.TTLI/OPQ2 (15)11EPI0S22

EPI module 0 signal 23.TTLI/OPQ3 (15)27EPI0S23

EPI module 0 signal 24.TTLI/OPK7 (15)60EPI0S24

EPI module 0 signal 25.TTLI/OPK6 (15)61EPI0S25

EPI module 0 signal 26.TTLI/OPL4 (15)85EPI0S26

EPI module 0 signal 27.TTLI/OPB2 (15)91EPI0S27

EPI module 0 signal 28.TTLI/OPB3 (15)92EPI0S28

EPI module 0 signal 29.TTLI/OPP2 (15)

PN2 (15)

103

109

EPI0S29

EPI module 0 signal 30.TTLI/OPP3 (15)

PN3 (15)

104

110

EPI0S30

EPI module 0 signal 31.TTLI/OPK5 (15)62EPI0S31

EPI module 0 signal 32.TTLI/OPK4 (15)63EPI0S32

EPI module 0 signal 33.TTLI/OPL5 (15)86EPI0S33

EPI module 0 signal 34.TTLI/OPN4 (15)111EPI0S34

EPI module 0 signal 35.TTLI/OPN5 (15)112EPI0S35

11.3 Functional Description

The EPI controller provides a glueless, programmable interface to a variety of common external

peripherals such as SDRAM x 16, Host Bus x8 and x16 devices, RAM, NOR Flash memory, CPLDs

and FPGAs. In addition, the EPI controller provides custom GPIO that can use a FIFO with speed

control by using either the internal write FIFO (WFIFO) or the non-blocking read FIFO (NBRFIFO).

The WFIFO can hold 4 words of data that are written to the external interface at the rate controlled

by the EPI Main Baud Rate (EPIBAUD) registers. The NBRFIFO can hold 8 words of data and

samples at the rate controlled by the EPIBAUD register. The EPI controller provides predictable

operation and thus has an advantage over regular GPIO which has more variable timing due to

on-chip bus arbitration and delays across bus bridges. Blocking reads stall the CPU until the

transaction completes. Non-blocking reads are performed in the background and allow the processor

June 18, 2014818

Texas Instruments-Production Data

External Peripheral Interface (EPI)

Loading...

Loading...