3. Set the MODE bit to 0x1 and the FSSHLDFM bit to 1 in the SSICR1 register. To operate in the

master mode, program the MS bit to 0. Program the remaining bits in the SSICR0 and SSICR1

register to relevant values.

4. Fill the Tx FIFO with one data byte.

5. Set the EOM bit in the SSICR1 register.

6. Fill the Tx FIFO with one data byte.

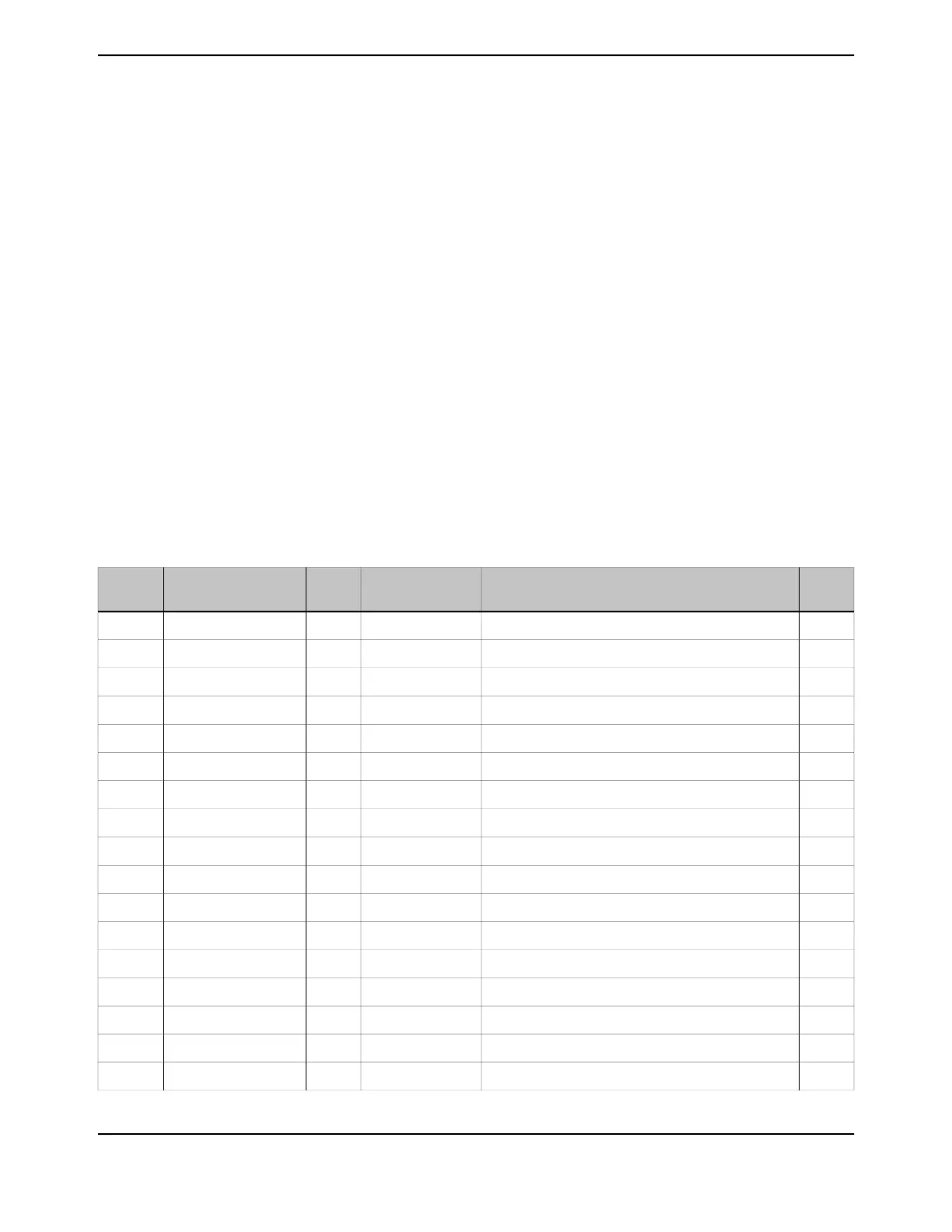

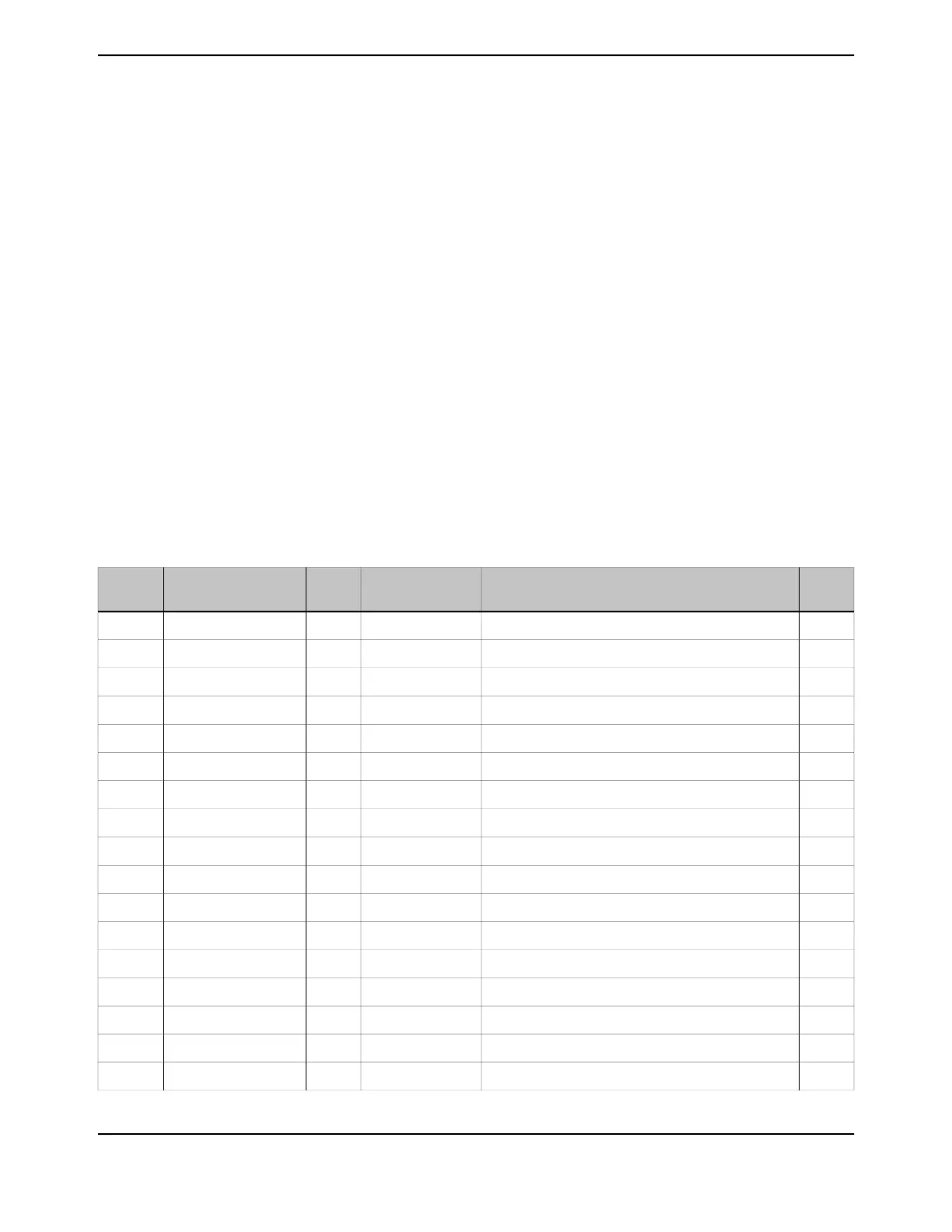

17.5 Register Map

Table 17-5 on page 1243 lists the QSSI registers. The offset listed is a hexadecimal increment to the

register’s address, relative to that QSSI module’s base address:

■ QSSI0: 0x4000.8000

■ QSSI1: 0x4000.9000

■ QSSI2: 0x4000.A000

■ QSSI3: 0x4000.B000

Note that the QSSI module clock must be enabled before the registers can be programmed (see

page 390). The Rn bit of the PRSSI register must be read as 0x1 before any QSSI module registers

are accessed.

Table 17-5. SSI Register Map

See

page

DescriptionResetTypeNameOffset

1245QSSI Control 00x0000.0000RWSSICR00x000

1247QSSI Control 10x0000.0000RWSSICR10x004

1249QSSI Data0x0000.0000RWSSIDR0x008

1250QSSI Status0x0000.0003ROSSISR0x00C

1252QSSI Clock Prescale0x0000.0000RWSSICPSR0x010

1253QSSI Interrupt Mask0x0000.0000RWSSIIM0x014

1255QSSI Raw Interrupt Status0x0000.0008ROSSIRIS0x018

1257QSSI Masked Interrupt Status0x0000.0000ROSSIMIS0x01C

1259QSSI Interrupt Clear0x0000.0000W1CSSIICR0x020

1260QSSI DMA Control0x0000.0000RWSSIDMACTL0x024

1261QSSI Peripheral Properties0x0000.000DROSSIPP0xFC0

1262QSSI Clock Configuration0x0000.0000RWSSICC0xFC8

1263QSSI Peripheral Identification 40x0000.0000ROSSIPeriphID40xFD0

1264QSSI Peripheral Identification 50x0000.0000ROSSIPeriphID50xFD4

1265QSSI Peripheral Identification 60x0000.0000ROSSIPeriphID60xFD8

1266QSSI Peripheral Identification 70x0000.0000ROSSIPeriphID70xFDC

1267QSSI Peripheral Identification 00x0000.0022ROSSIPeriphID00xFE0

1243June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...