Register 39: Ethernet MAC Sub-Second Increment (EMACSUBSECINC), offset

0x704

In the Coarse Update mode (enabled by the TSCFUPDT bit in the MAC Timestamp Control

(EMACTIMSTCTRL) register), the value in the EMACSUBSECINC register is added to the system

time every clock cycle of slave clock reference, MOSC. In the Fine Update mode, the value in this

register is added to the system time whenever the Accumulator gets an overflow.

Ethernet MAC Sub-Second Increment (EMACSUBSECINC)

Base 0x400E.C000

Offset 0x704

Type RW, reset 0x0000.0000

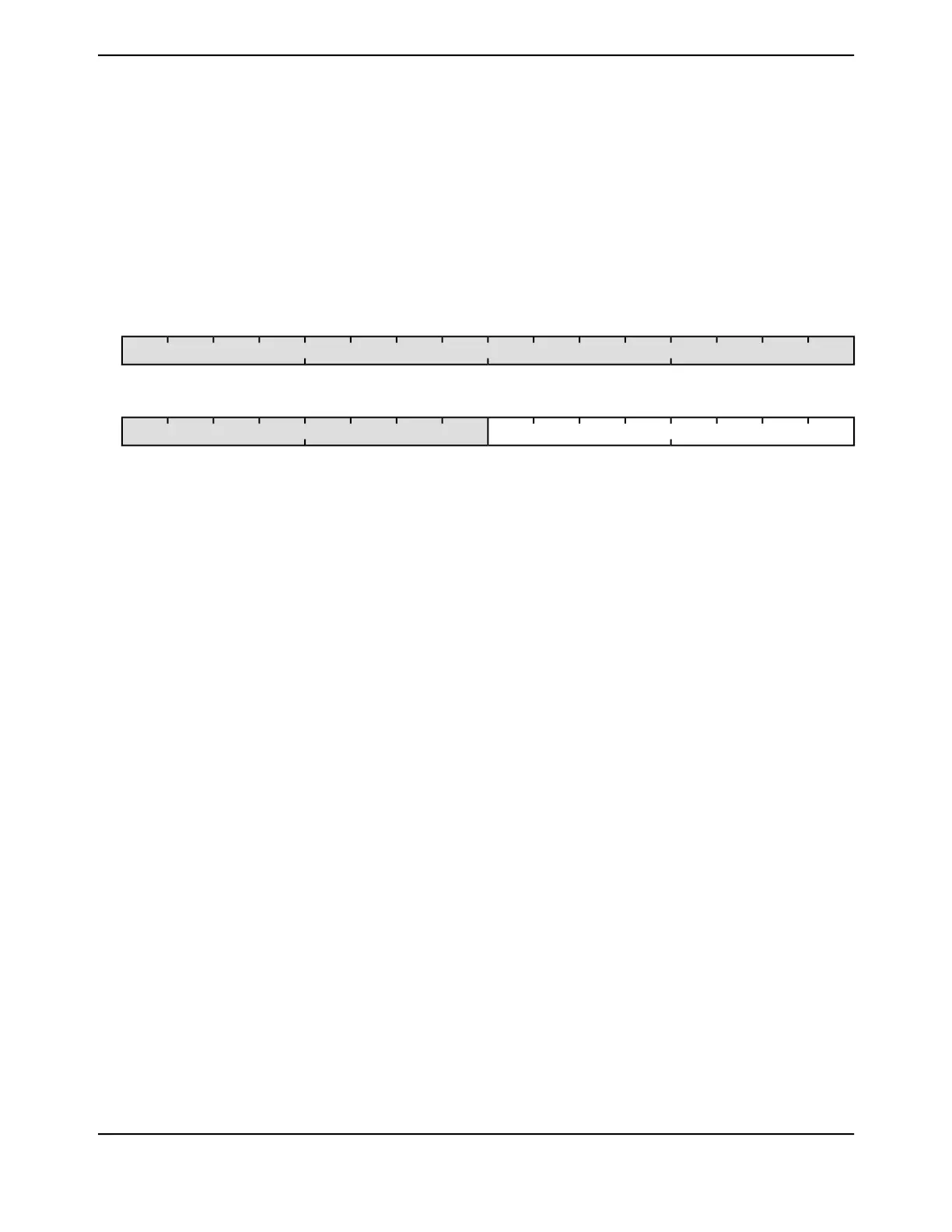

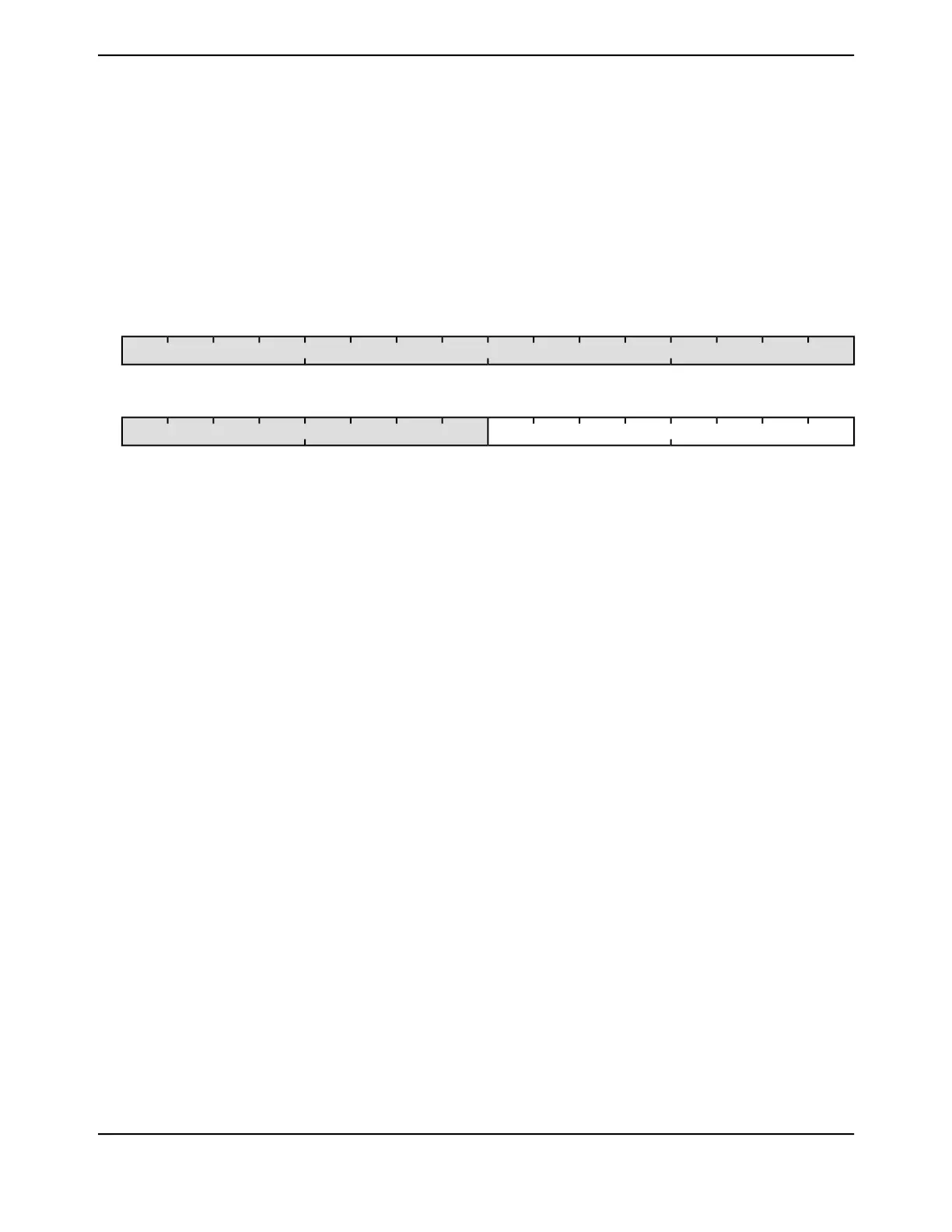

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

0123456789101112131415

SSINCreserved

RWRWRWRWRWRWRWRWROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved31:8

Sub-second Increment Value

The value programmed in this field is accumulated every clock cycle

(MOSC) with the contents of the sub-second register. For example,

when MOSC is 25 MHz (period is 40 ns), SSINC should be programmed

with the value 40 (0x28) when the Ethernet MAC System Time -

Nanoseconds (EMACTIMNANO) register has an accuracy of 1 ns

(DGTLBIN bit is set in EMACTIMSTCTRL). When DGTLBIN bit is clear,

the EMACTIMNANO register has a resolution of ~0.465ns. In this case,

a value of 86 (0x56), that is derived by 40ns/0.465, should be

programmed in the SSINC field.

0x0RWSSINC7:0

June 18, 20141538

Texas Instruments-Production Data

Ethernet Controller

Loading...

Loading...