Register 22: GPTM RTC Predivide (GPTMRTCPD), offset 0x058

This register provides the current RTC predivider value when the timer is operating in RTC mode.

Software must perform an atomic access with consecutive reads of the GPTMTAR, GPTMTBR,

and GPTMRTCPD registers.

Note: When an alternate clock source is enabled, a read of this register returns the current count

-1.

GPTM RTC Predivide (GPTMRTCPD)

16/32-bit Timer 0 base: 0x4003.0000

16/32-bit Timer 1 base: 0x4003.1000

16/32-bit Timer 2 base: 0x4003.2000

16/32-bit Timer 3 base: 0x4003.3000

16/32-bit Timer 4 base: 0x4003.4000

16/32-bit Timer 5 base: 0x4003.5000

16/32-bit Timer 6 base: 0x400E.0000

16/32-bit Timer 7 base: 0x400E.1000

Offset 0x058

Type RO, reset 0x0000.7FFF

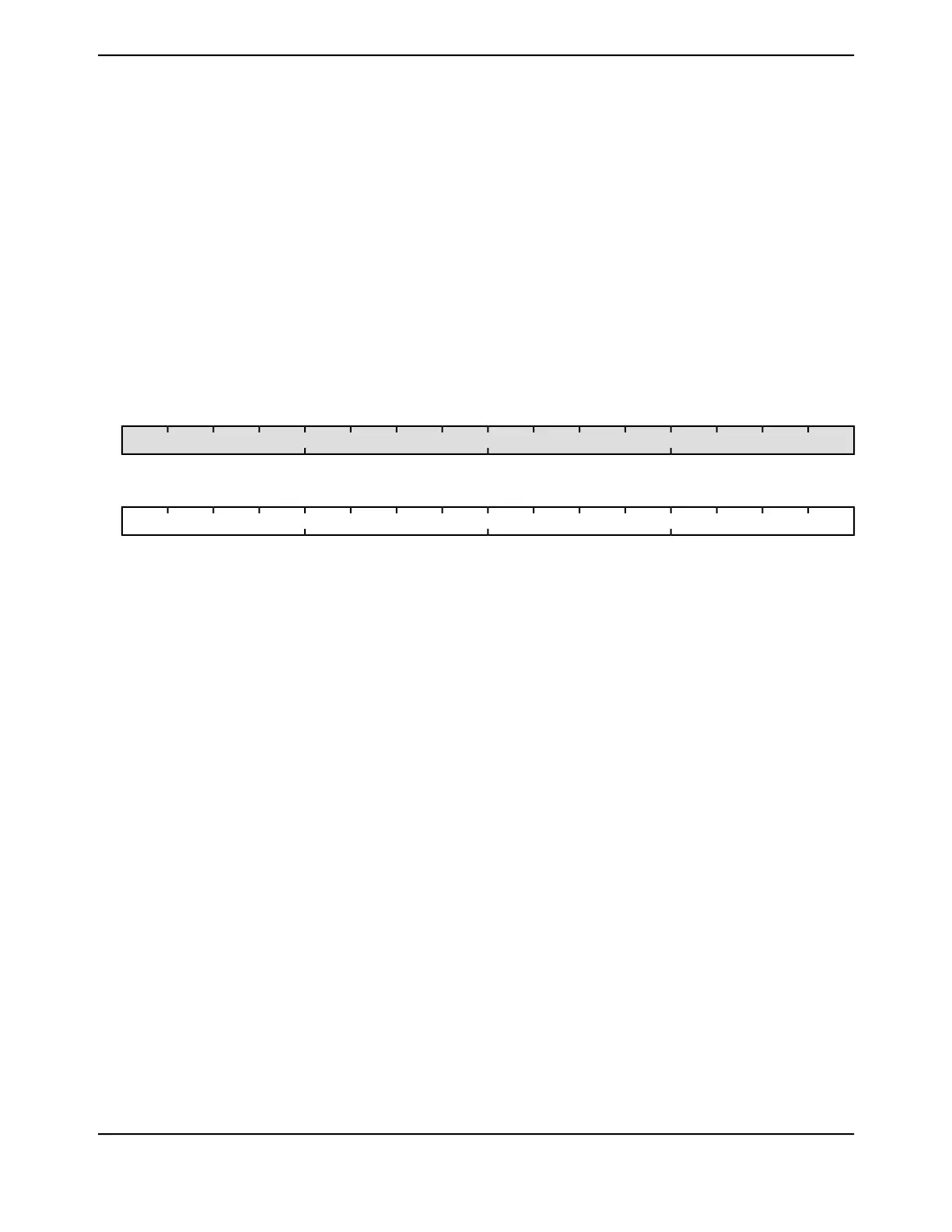

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

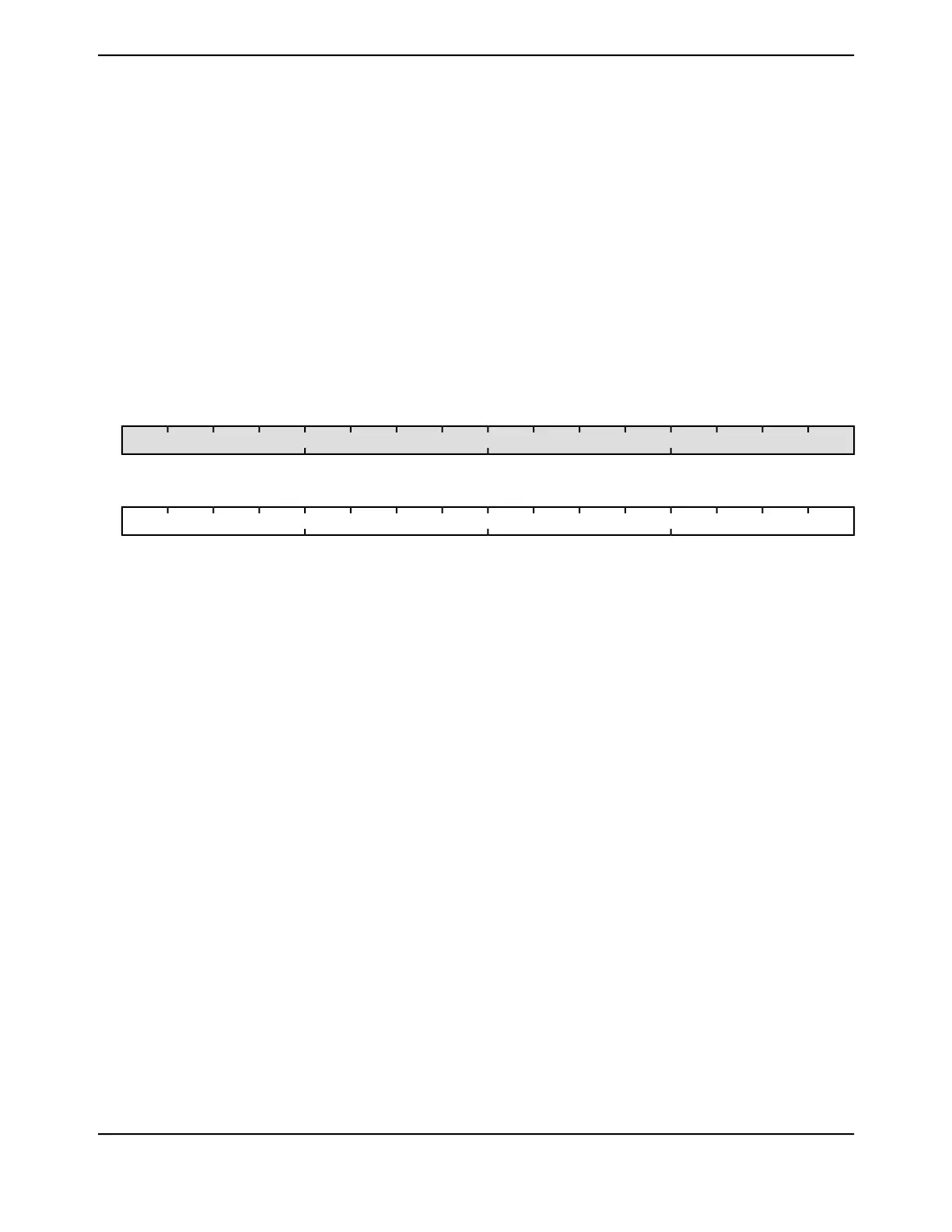

0123456789101112131415

RTCPD

ROROROROROROROROROROROROROROROROType

1111111111111110Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000ROreserved31:16

RTC Predivide Counter Value

The current RTC predivider value when the timer is operating in RTC

mode. This field has no meaning in other timer modes.

0x0000.7FFFRORTCPD15:0

June 18, 20141016

Texas Instruments-Production Data

General-Purpose Timers

Loading...

Loading...