Register 23: DMA Channel Map Select 1 (DMACHMAP1), offset 0x514

Each 4-bit field of the DMACHMAP1 register configures the μDMA channel assignment as specified

in Table 9-1 on page 680.

Note: To support legacy software which uses the DMA Channel Assignment (DMACHASGN)

register, a value of 0x0 is equivalent to a DMACHASGN bit being clear, and a value of 0x1

is equivalent to a DMACHASGN bit being set.

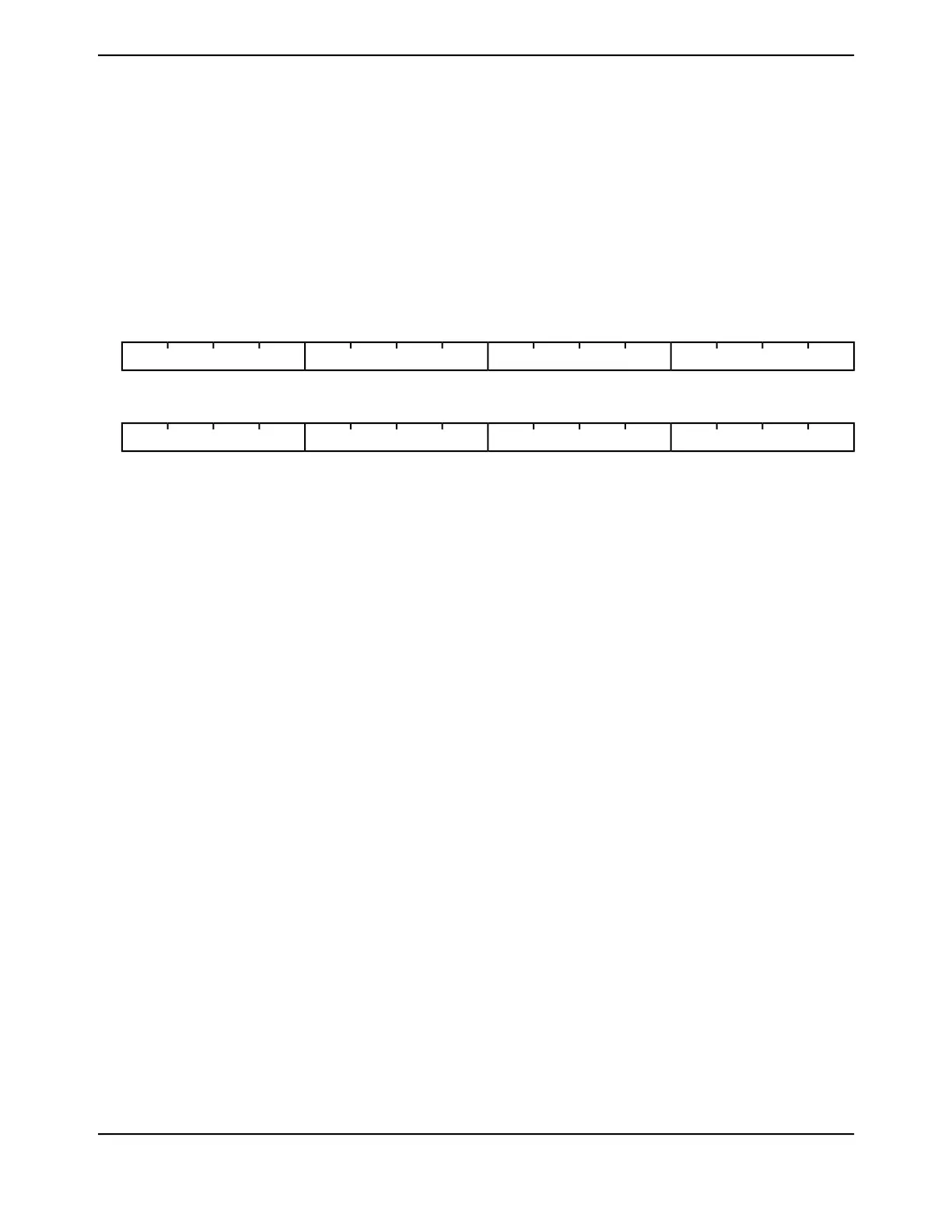

DMA Channel Map Select 1 (DMACHMAP1)

Base 0x400F.F000

Offset 0x514

Type RW, reset 0x0000.0000

16171819202122232425262728293031

CH12SELCH13SELCH14SELCH15SEL

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWRWType

0000000000000000Reset

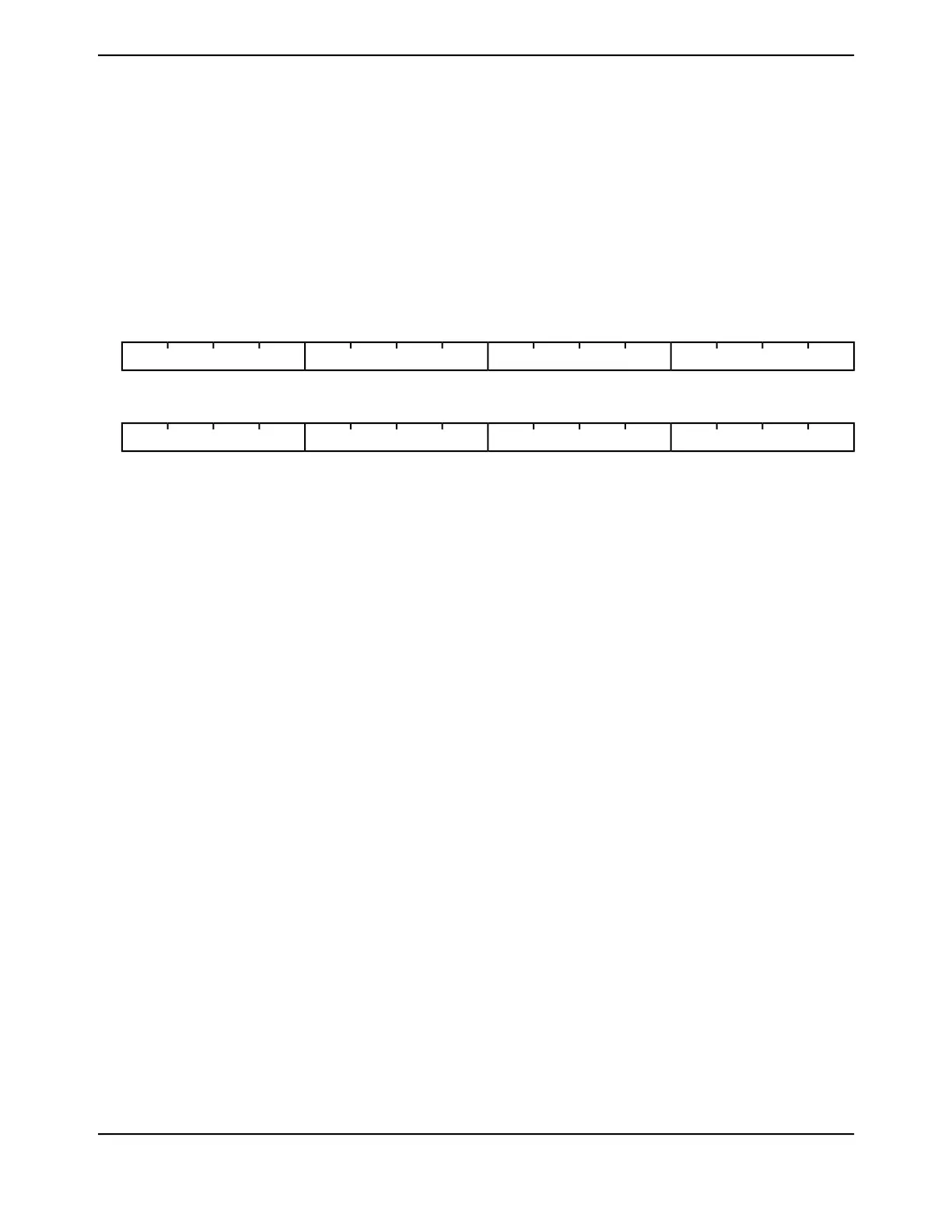

0123456789101112131415

CH8SELCH9SELCH10SELCH11SEL

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWRWType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

μDMA Channel 15 Source Select

See Table 9-1 on page 680 for channel assignments.

0x00RWCH15SEL31:28

μDMA Channel 14 Source Select

See Table 9-1 on page 680 for channel assignments.

0x00RWCH14SEL27:24

μDMA Channel 13 Source Select

See Table 9-1 on page 680 for channel assignments.

0x00RWCH13SEL23:20

μDMA Channel 12 Source Select

See Table 9-1 on page 680 for channel assignments.

0x00RWCH12SEL19:16

μDMA Channel 11 Source Select

See Table 9-1 on page 680 for channel assignments.

0x00RWCH11SEL15:12

μDMA Channel 10 Source Select

See Table 9-1 on page 680 for channel assignments.

0x00RWCH10SEL11:8

μDMA Channel 9 Source Select

See Table 9-1 on page 680 for channel assignments.

0x00RWCH9SEL7:4

μDMA Channel 8 Source Select

See Table 9-1 on page 680 for channel assignments.

0x00RWCH8SEL3:0

June 18, 2014730

Texas Instruments-Production Data

Micro Direct Memory Access (μDMA)

Loading...

Loading...