Register 5: EPI Host-Bus 8 Configuration (EPIHB8CFG), offset 0x010

Important: The MODE field in the EPICFG register determines which configuration register is

accessed for offsets 0x010 and 0x014.

To access EPIHB8CFG, the MODE field must be 0x2.

The Host Bus 8 Configuration register is activated when the HB8 mode is selected. The HB8 mode

supports muxed address/data (overlay of lower 8 address and all 8 data pins), separate address/data,

and address-less FIFO mode. Note that this register is reset when the MODE field in the EPICFG

register is changed. If another mode is selected and the HB8 mode is selected again, the values

must be reinitialized.

This mode is intended to support SRAMs, Flash memory (read), FIFOs, CPLDs/FPGAs, and devices

with an MCU/HostBus slave or 8-bit FIFO interface support.

Refer to Table 11-8 on page 831 for information on signal configuration controlled by this register

and the EPIHB8CFG2 register.

If less address pins are required, the corresponding AFSEL bit (page 770) should not be enabled so

the EPI controller does not drive those pins, and they are available as standard GPIOs.

EPI Host-Bus 8 Mode can be configured to use one to four chip selects with and without the use of

ALE. If an alternative to chip selects are required, a chip enable can be handled in one of three

ways:

1. Manually control via GPIOs.

2. Associate one or more upper address pins to CE. Because CE is normally CEn, lower addresses

are not used. For example, if pins EPI0S27 and EPI0S26 are used for Device 1 and 0

respectively, then address 0x6800.0000 accesses Device 0 (Device 1 has its CEn high), and

0x6400.0000 accesses Device 1 (Device 0 has its CEn high). The pull-up behavior on the

corresponding GPIOs must be properly configured to ensure that the pins are disabled when

the interface is not in use.

3. With certain SRAMs, the ALE can be used as CEn because the address remains stable after

the ALE strobe. The subsequent WRn or RDn signals write or read when ALE is low thus

providing CEn functionality.

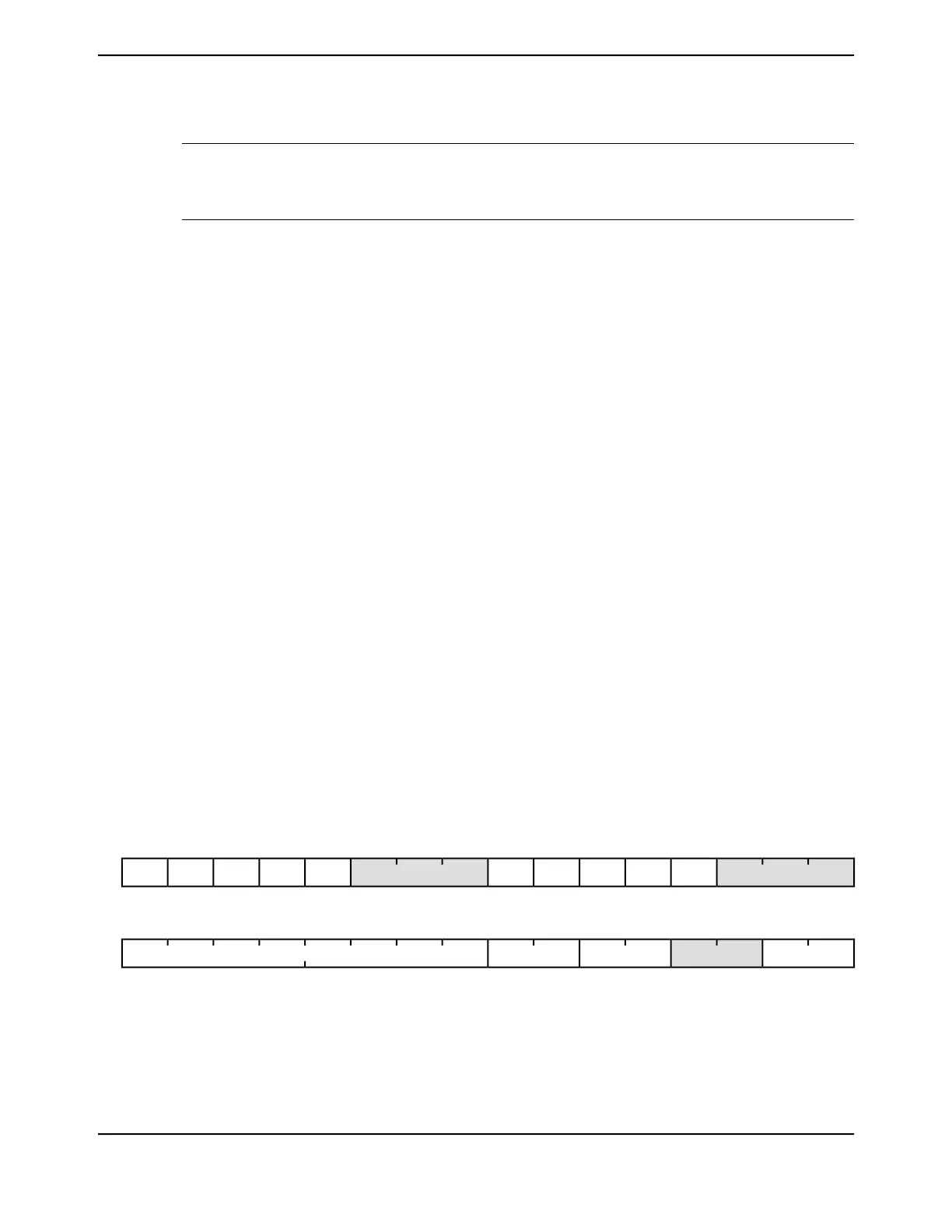

EPI Host-Bus 8 Configuration (EPIHB8CFG)

Base 0x400D.0000

Offset 0x010

Type RW, reset 0x0008.FF00

16171819202122232425262728293031

reservedALEHIGHRDHIGHWRHIGHXFEENXFFENreservedIRDYINVRDYENCLKINV

CLKGATEI

CLKGATE

RORORORWRWRWRWRWRORORORWRWRWRWRWType

0001000000000000Reset

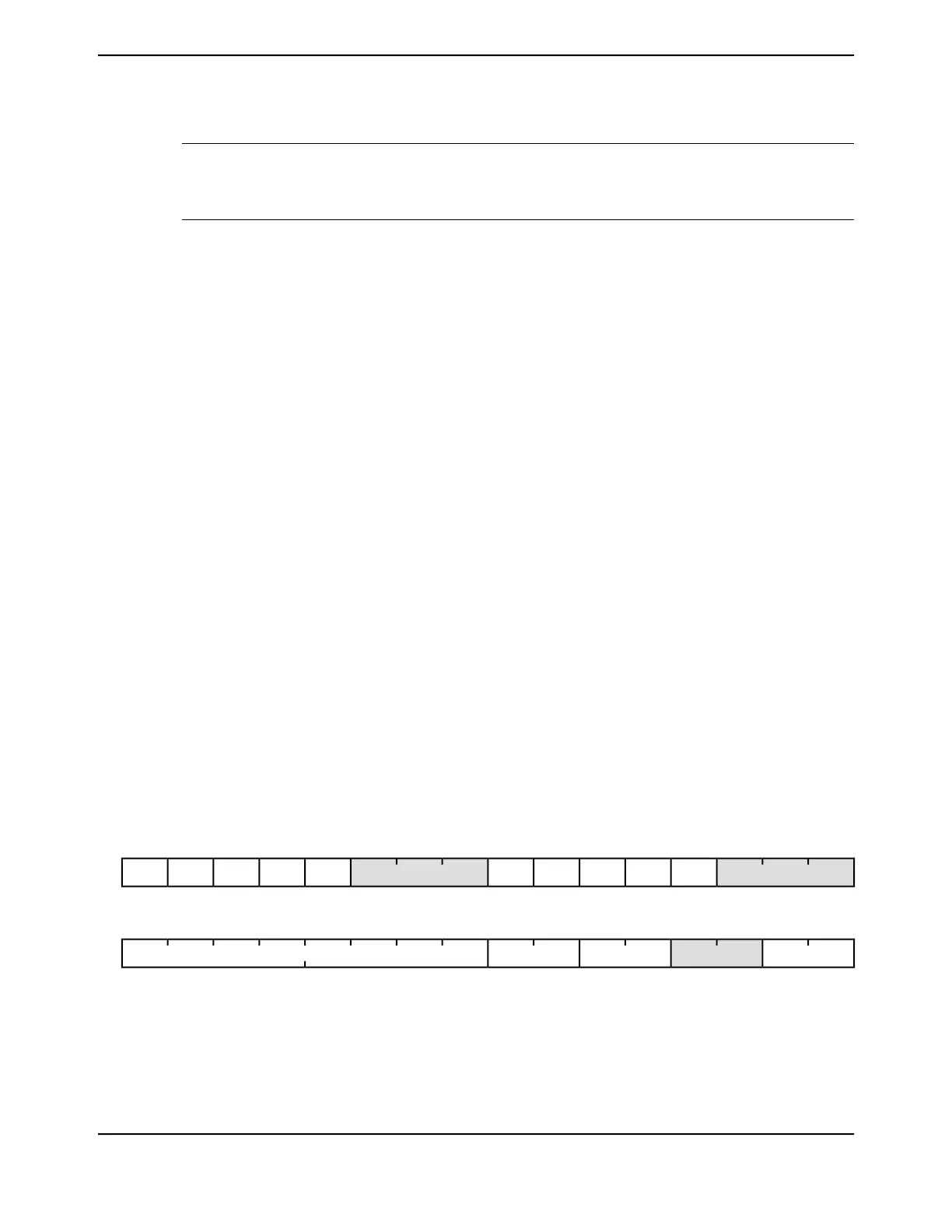

0123456789101112131415

MODEreservedRDWSWRWSMAXWAIT

RWRWRORORWRWRWRWRWRWRWRWRWRWRWRWType

0000000011111111Reset

865June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...