Register 22: HIB Tamper Status (HIBTPSTAT), offset 0x404

The HIB Tamper Status (HIBTPCTL) register provides status of the module.

Note: Except for the HIBIO and a portion of the HIBIC register, all other Hibernation module

registers are on the Hibernation module clock domain and have special timing requirements.

Software should make use of the WRC bit in the HIBCTL register to ensure that the required

timing gap has elapsed. If the WRC bit is clear, any attempted write access is ignored. See

“Register Access Timing” on page 535. The HIBIO register and bits RSTWK, PADIOWK and

WC of the HIBIC register do not require waiting for write to complete. Because these registers

are clocked by the system clock, writes to these registers/bits are immediate.

Writing to registers other than the HIBCTL and HIBIM before the CLK32EN bit in the HIBCTL

register has been set may produce unexpected results.

Note: Errant writes to the Tamper registers are protected by the Hibernate HIBLOCK register.

HIB Tamper Status (HIBTPSTAT)

Base 0x400F.C000

Offset 0x404

Type RW1C, reset 0x0000.0000

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

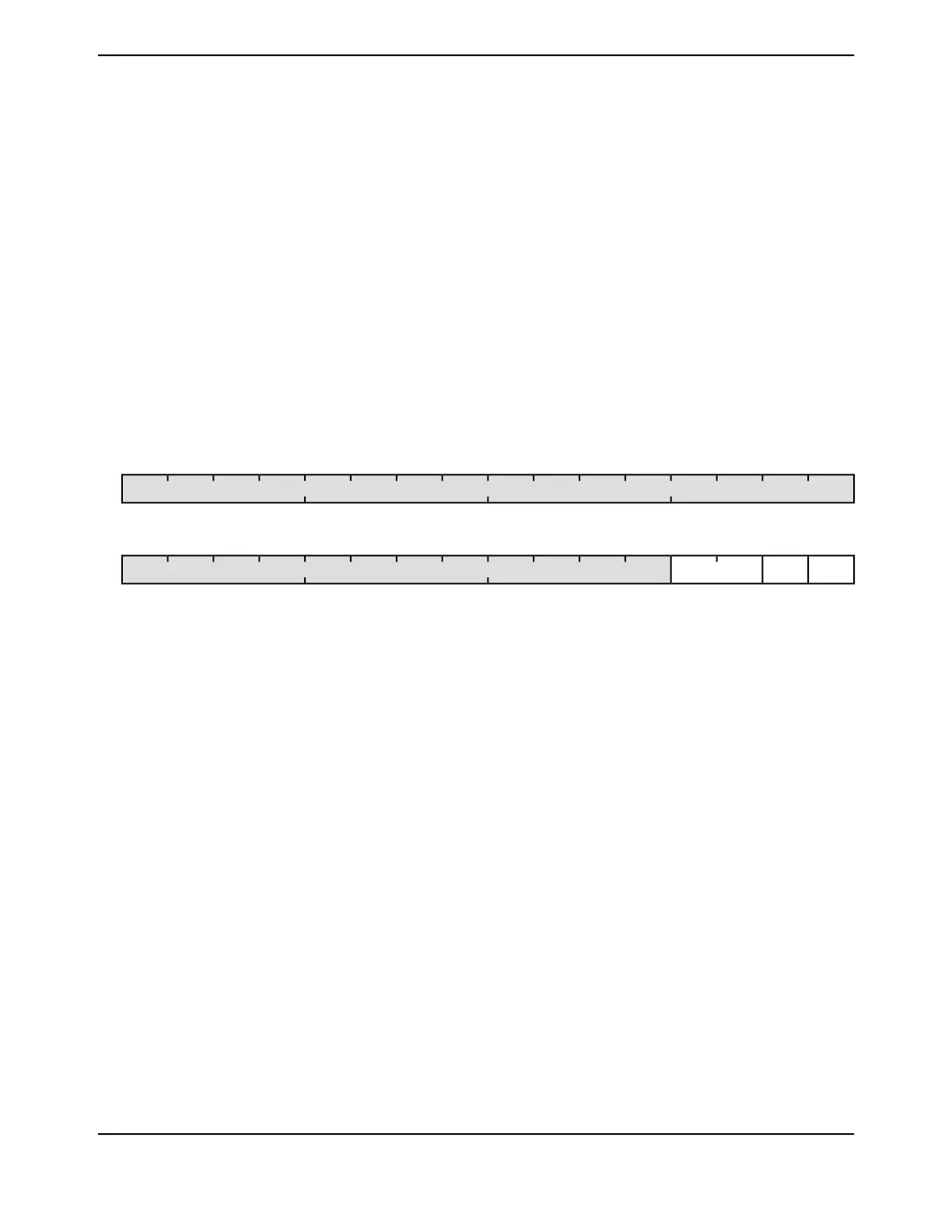

0123456789101112131415

XOSCFAIL

XOSCSTSTATEreserved

RW1CROROROROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0ROreserved31:4

Tamper Module Status

Tamper is defined as being configured when the tamper I/Os have been

enabled (setting the ENx bits in the HIBTPIO register).

DescriptionValue

Tamper disabled.0x0

Tamper configured.0x1

Tamper pin event occurred.0x2

0ROSTATE3:2

External Oscillator Status

DescriptionValue

Active0

Stopped1

0ROXOSCST1

589June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...