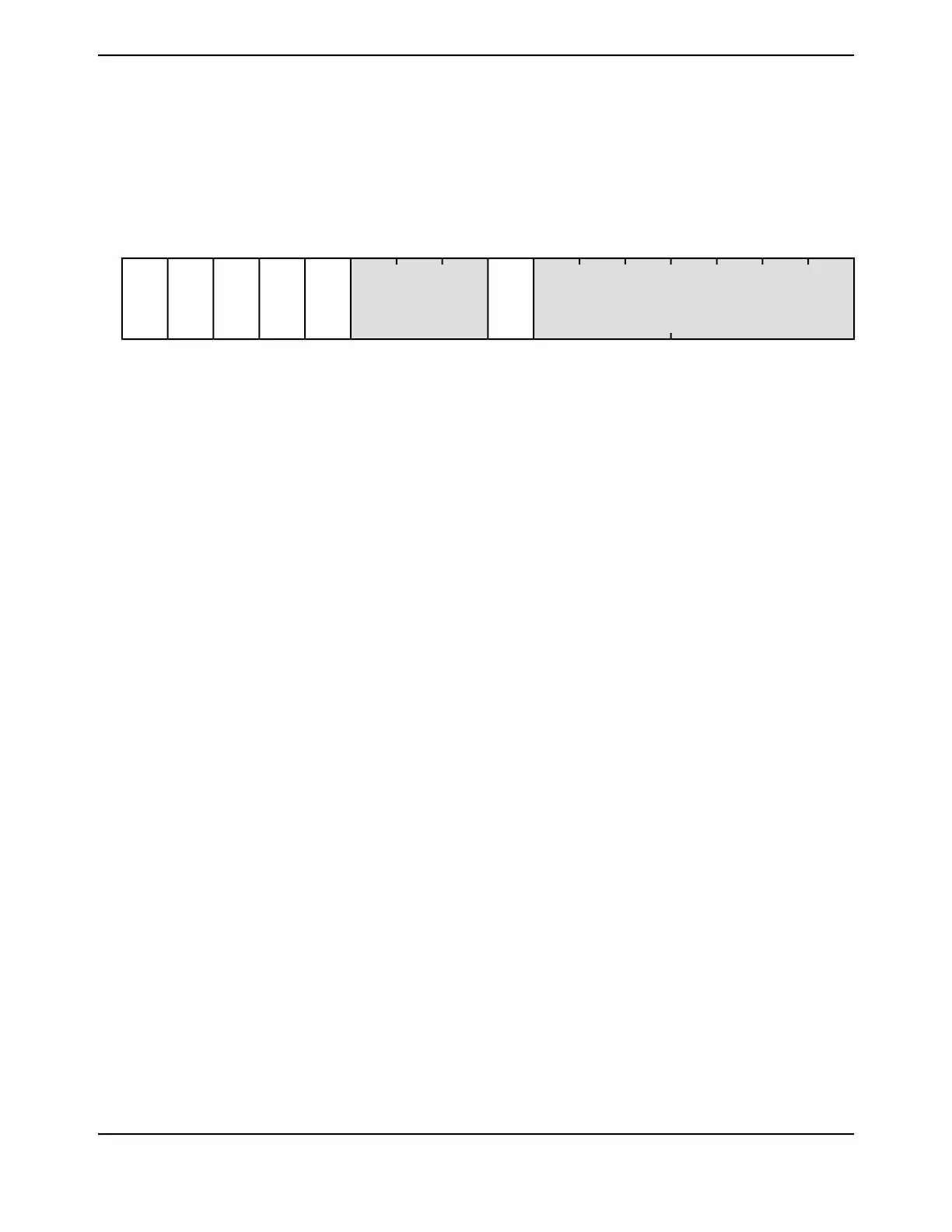

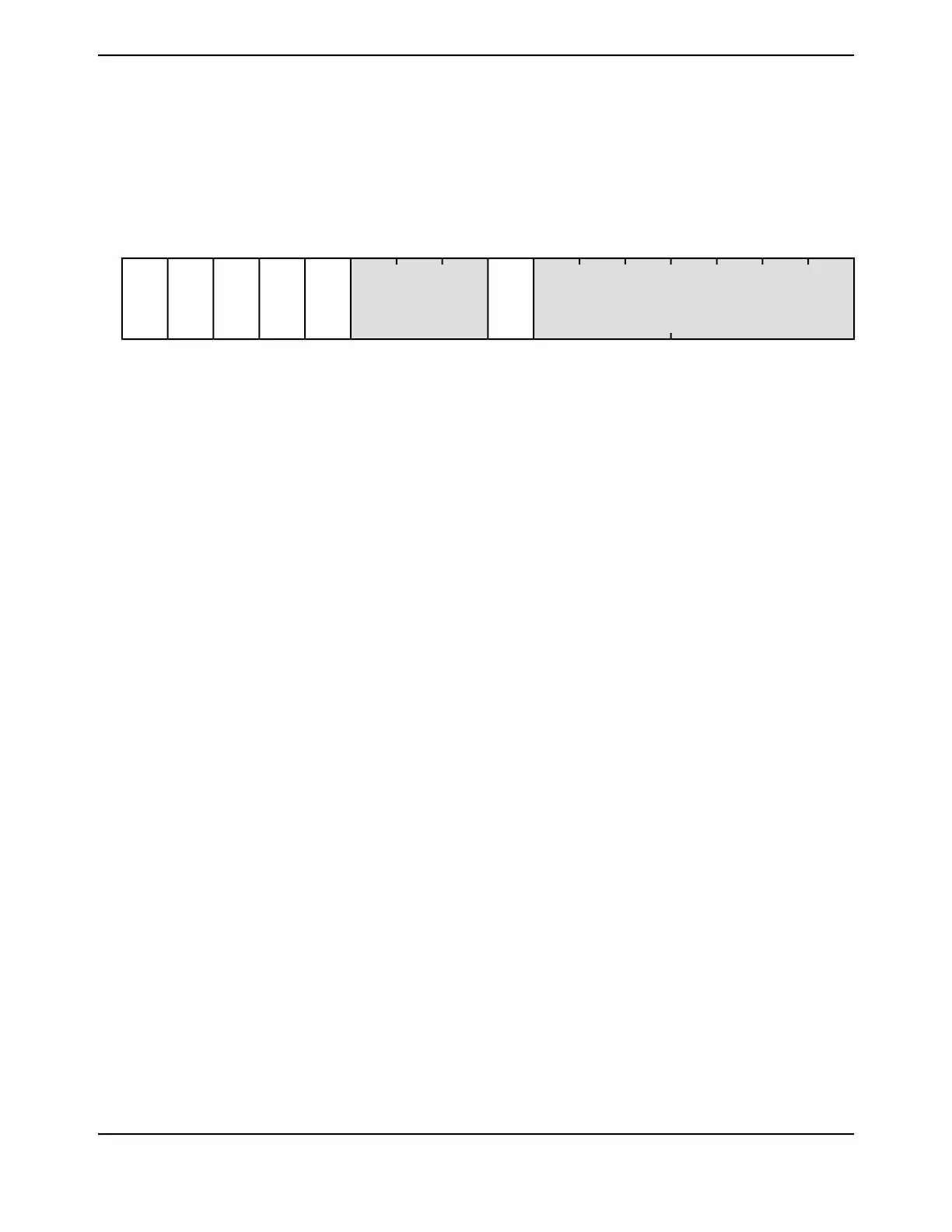

Register 94: Ethernet PHY Control - MR25 (EPHYCTL), address 0x019

This register provides the ability to control and set general functionality inside the PHY.

Ethernet PHY Control - MR25 (EPHYCTL)

Base n/a

Address 0x019

Type RW, reset 0x8000

0123456789101112131415

reserved

BYPLEDSTRCH

reserved

MIILNKSTAT

PAUSETXPAUSERX

FORCEMDI

AUTOMDI

RORORORORORORORWRORORORORORORWRWType

0000000000000001Reset

DescriptionResetTypeNameBit/Field

Auto-MDIX Enable

DescriptionValue

Disable Auto- negotiation, Auto-MDIX capability.0

Enable Auto-negotiation, Auto-MDIX capability.1

1RWAUTOMDI15

Force MDIX

DescriptionValue

Normal operation. (Transmit on TPTD pair, Receive on TPRD

pair)

0

Force MDI pairs to cross. (Receive on TPTD pair, Transmit on

TPRD pair)

1

0RWFORCEMDI14

Pause Receive Negotiated Status

DescriptionValue

No effect.0

Indicates that pause receive should be enabled in the MAC.

This bit is set based on bits [11:10] in the EPHYANA register

and in the EPHYANLPAR register settings.

This function is enabled according to IEEE 802.3 Annex 28B

Table 28B-3, Pause Resolution, only if the Auto-Negotiated

Highest Common Denominator is a full-duplex technology.

1

0ROPAUSERX13

Pause Transmit Negotiated Status

DescriptionValue

No effect.0

Indicates that pause transmit should be enabled in the MAC.

This bit is set based on bits [11:10] in the EPHYANA register

and in the EPHYANLPAR register settings.

This function is enabled according to IEEE 802.3 Annex 28B

Table 28B-3, Pause Resolution, only if the Auto-Negotiated

Highest Common Denominator is a full-duplex technology.

1

0ROPAUSETX12

June 18, 20141634

Texas Instruments-Production Data

Ethernet Controller

Loading...

Loading...