Register 4: I

2

C Master Timer Period (I2CMTPR), offset 0x00C

This register is programmed to set the timer period for the SCL clock and assign the SCL clock to

either standard or high-speed mode.

I2C Master Timer Period (I2CMTPR)

I2C 0 base: 0x4002.0000

I2C 1 base: 0x4002.1000

I2C 2 base: 0x4002.2000

I2C 3 base: 0x4002.3000

I2C 4 base: 0x400C.0000

I2C 5 base: 0x400C.1000

I2C 6 base: 0x400C.2000

I2C 7 base: 0x400C.3000

I2C 8 base: 0x400B.8000

I2C 9 base: 0x400B.9000

Offset 0x00C

Type RW, reset 0x0000.0001

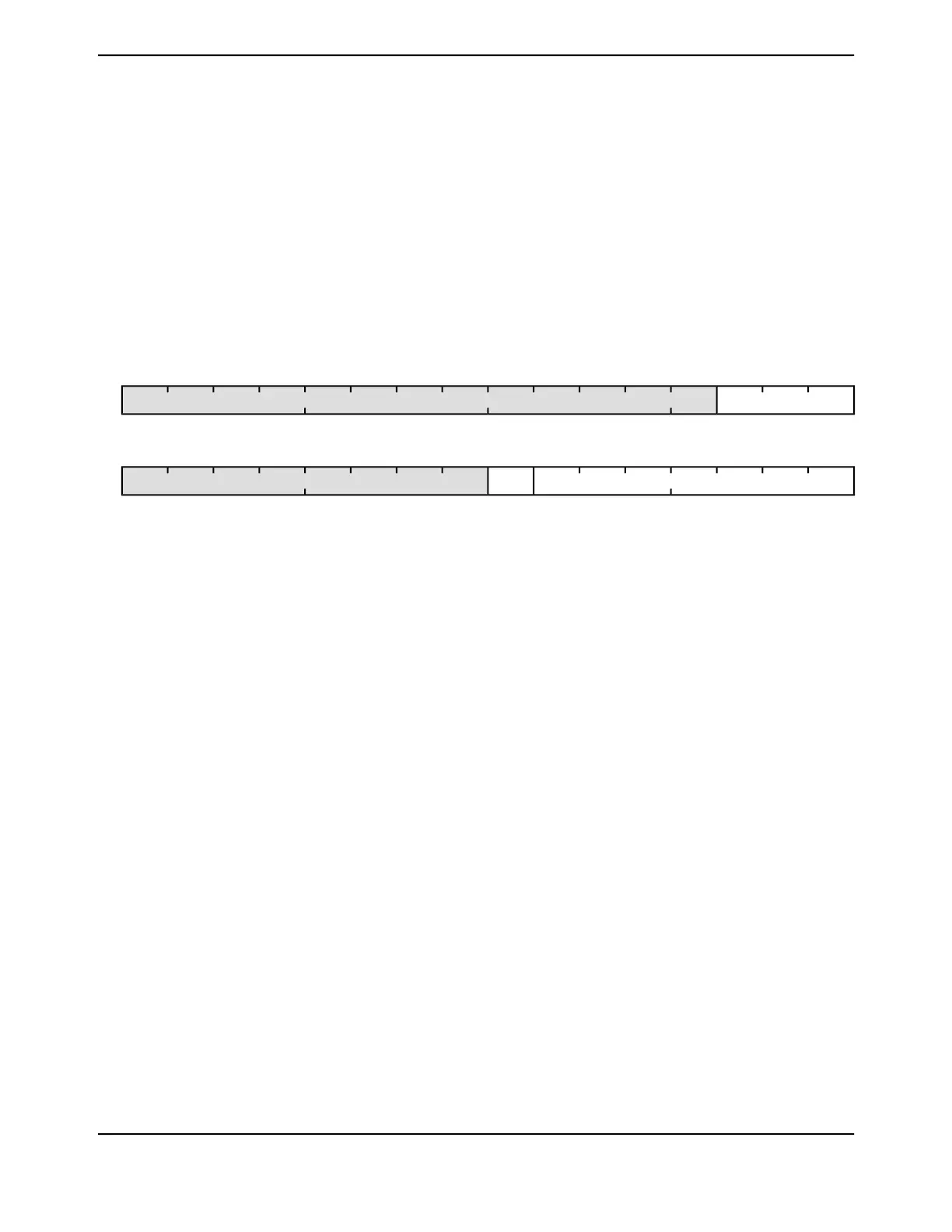

16171819202122232425262728293031

PULSELreserved

RWRWRWROROROROROROROROROROROROROType

0000000000000000Reset

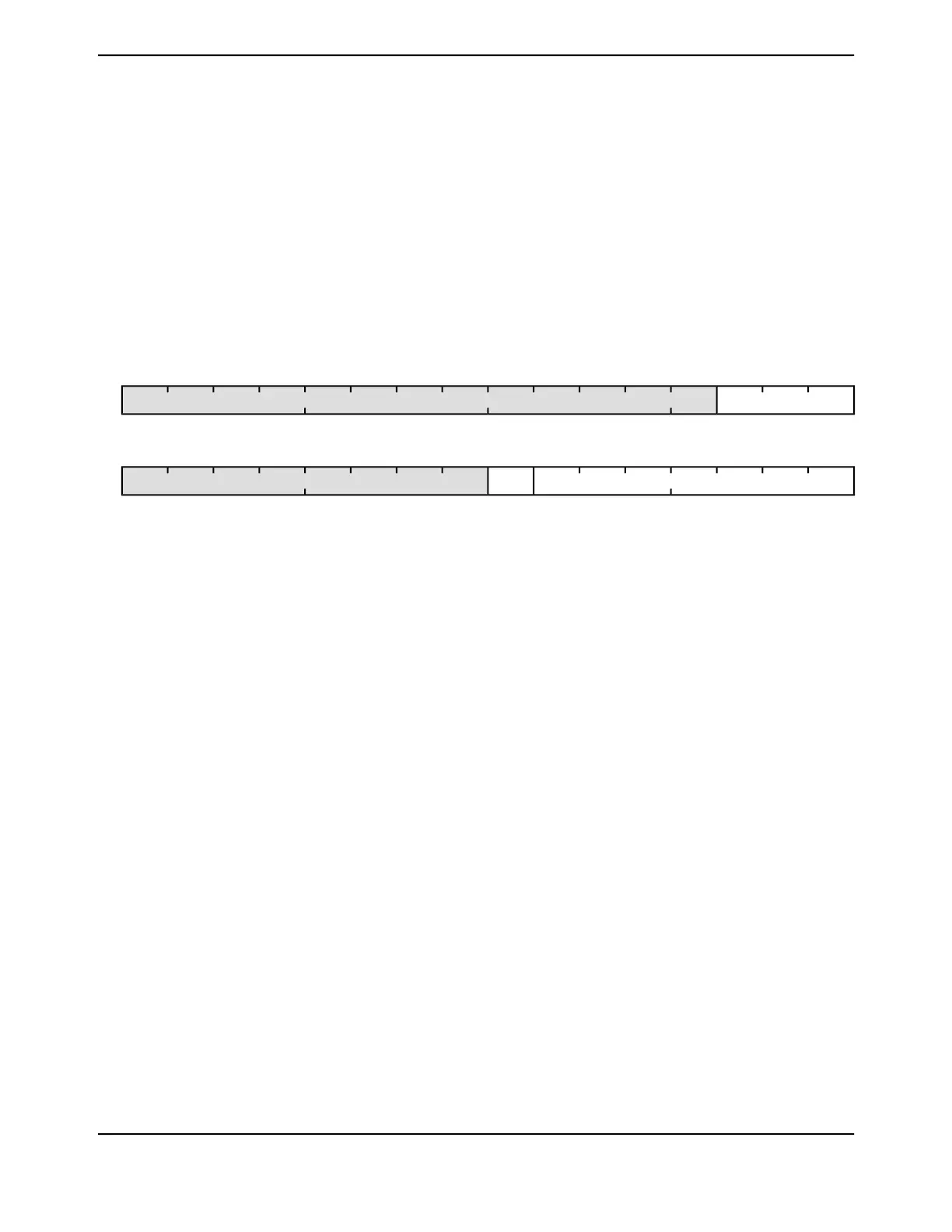

0123456789101112131415

TPRHSreserved

RWRWRWRWRWRWRWWOROROROROROROROROType

1000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.00ROreserved31:19

Glitch Suppression Pulse Width

This field controls the pulse width select for glitch suppression on the

SCL and SDA lines. The following values are the glitch suppression

values in terms of system clocks.

DescriptionValue

Bypass0x0

1 clock0x1

2 clocks0x2

3 clocks0x3

4 clocks0x4

8 clocks0x5

16 clocks0x6

31 clocks0x7

0x0RWPULSEL18:16

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.00ROreserved15:8

1313June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...