Register 24: PWM0 Interrupt Status and Clear (PWM0ISC), offset 0x04C

Register 25: PWM1 Interrupt Status and Clear (PWM1ISC), offset 0x08C

Register 26: PWM2 Interrupt Status and Clear (PWM2ISC), offset 0x0CC

Register 27: PWM3 Interrupt Status and Clear (PWM3ISC), offset 0x10C

These registers provide the current set of interrupt sources that are asserted to the interrupt controller

(PWM0ISC controls the PWM generator 0 block, and so on). A bit is set if the event has occurred

and is enabled in the PWMnINTEN register; if a bit is clear, the event has not occurred or is not

enabled. These are RW1C registers; writing a 1 to a bit position clears the corresponding interrupt

reason.

Note: The interrupt status can only be cleared one PWM Clock cycle after the interrupt occurs.

The larger the PWM Clock Divider (PWMDIV) value in PWMCC register, the longer the

system delay is to clear the interrupt.

PWMn Interrupt Status and Clear (PWMnISC)

PWM0 base: 0x4002.8000

Offset 0x04C

Type RW1C, reset 0x0000.0000

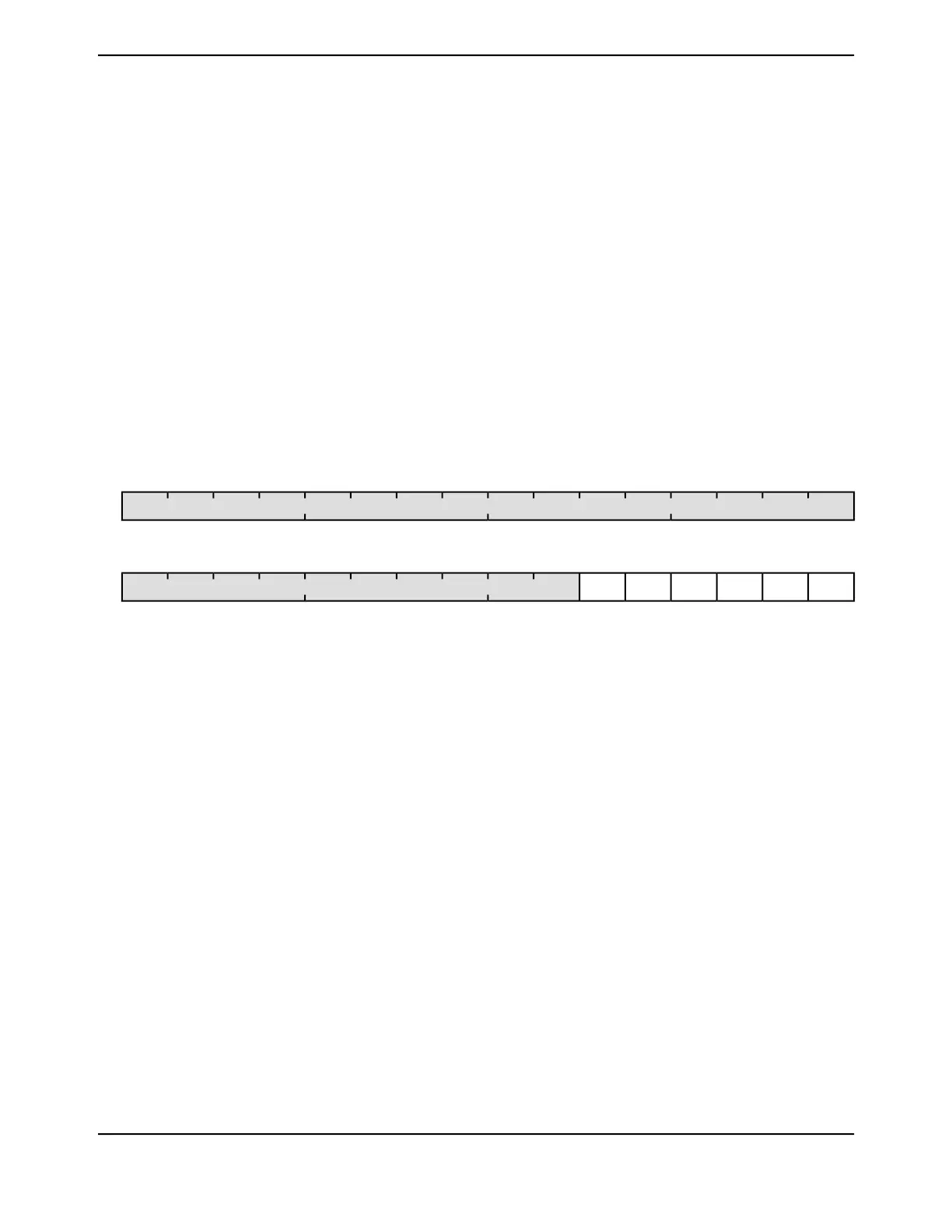

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

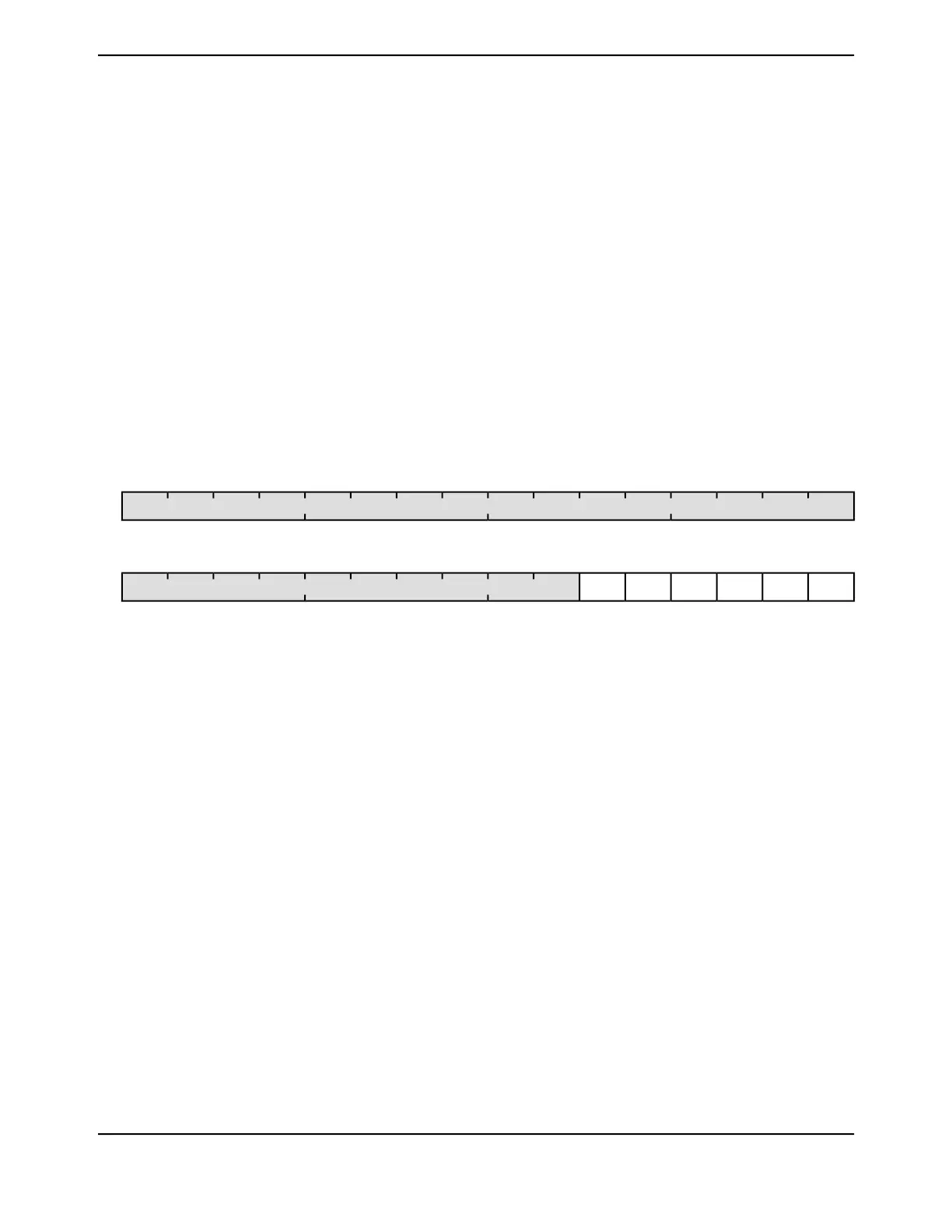

0123456789101112131415

INTCNTZEROINTCNTLOAD

INTCMPAUINTCMPADINTCMPBUINTCMPBD

reserved

RW1CRW1CRW1CRW1CRW1CRW1CROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0ROreserved31:6

Comparator B Down Interrupt

DescriptionValue

No interrupt has occurred or the interrupt is masked.0

The INTCMPBD bits in the PWMnRIS and PWMnINTEN registers

are set, providing an interrupt to the interrupt controller.

1

This bit is cleared by writing a 1. Clearing this bit also clears the

INTCMPBD bit in the PWMnRIS register.

0RW1CINTCMPBD5

Comparator B Up Interrupt

DescriptionValue

No interrupt has occurred or the interrupt is masked.0

The INTCMPBU bits in the PWMnRIS and PWMnINTEN registers

are set, providing an interrupt to the interrupt controller.

1

This bit is cleared by writing a 1. Clearing this bit also clears the

INTCMPBU bit in the PWMnRIS register.

0RW1CINTCMPBU4

June 18, 20141718

Texas Instruments-Production Data

Pulse Width Modulator (PWM)

Loading...

Loading...