Register 11: ADC Processor Sample Sequence Initiate (ADCPSSI), offset 0x028

This register provides a mechanism for application software to initiate sampling in the sample

sequencers. Sample sequences can be initiated individually or in any combination. When multiple

sequences are triggered simultaneously, the priority encodings in ADCSSPRI dictate execution

order.

This register also provides a means to configure and then initiate concurrent sampling on all ADC

modules. To do this, the first ADC module should be configured. The ADCPSSI register for that

module should then be written. The appropriate SS bits should be set along with the SYNCWAIT bit.

Additional ADC modules should then be configured following the same procedure. Once the final

ADC module is configured, its ADCPSSI register should be written with the appropriate SS bits set

along with the GSYNC bit. All of the ADC modules then begin concurrent sampling according to their

configuration.

ADC Processor Sample Sequence Initiate (ADCPSSI)

ADC0 base: 0x4003.8000

ADC1 base: 0x4003.9000

Offset 0x028

Type RW, reset -

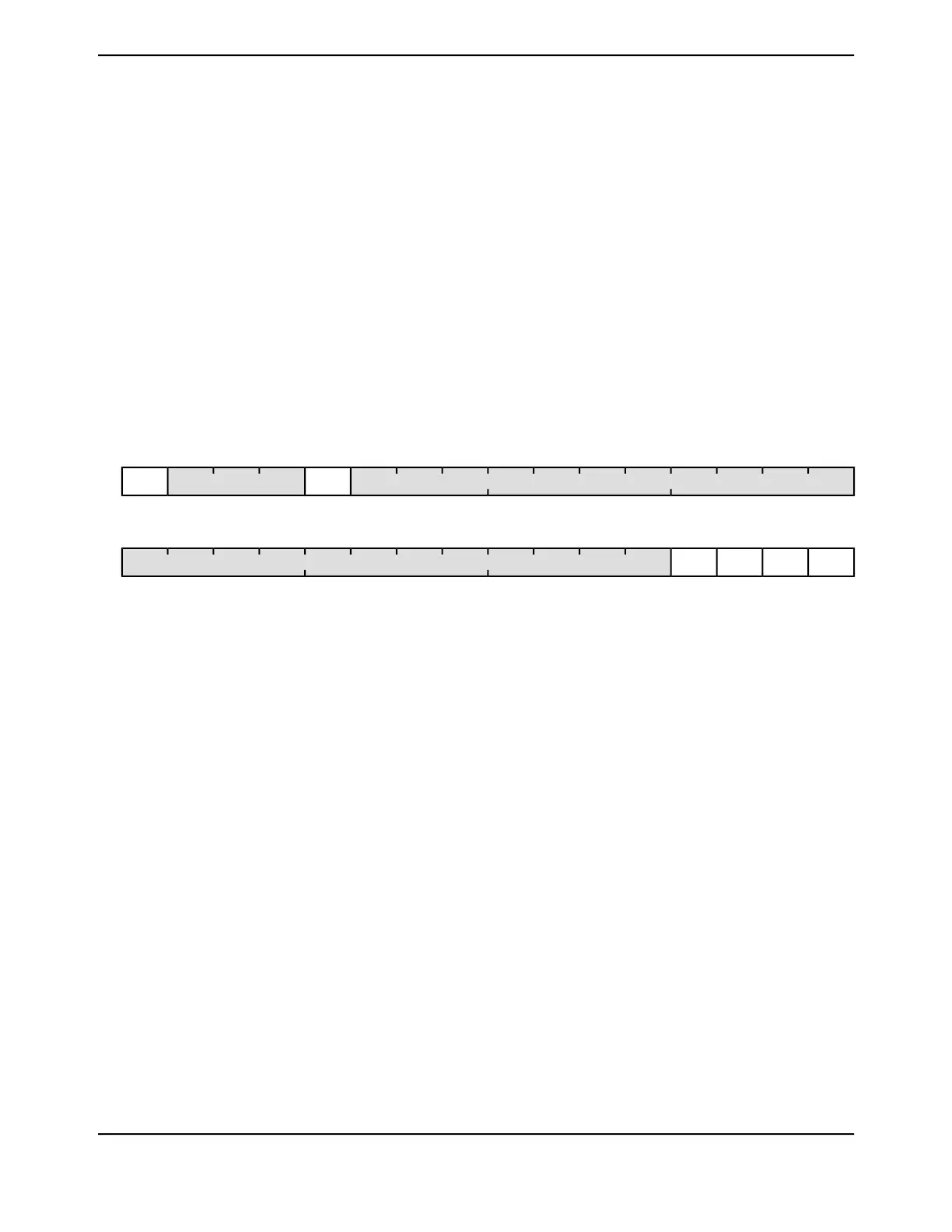

16171819202122232425262728293031

reserved

SYNCWAIT

reservedGSYNC

RORORORORORORORORORORORWRORORORWType

0000000000000000Reset

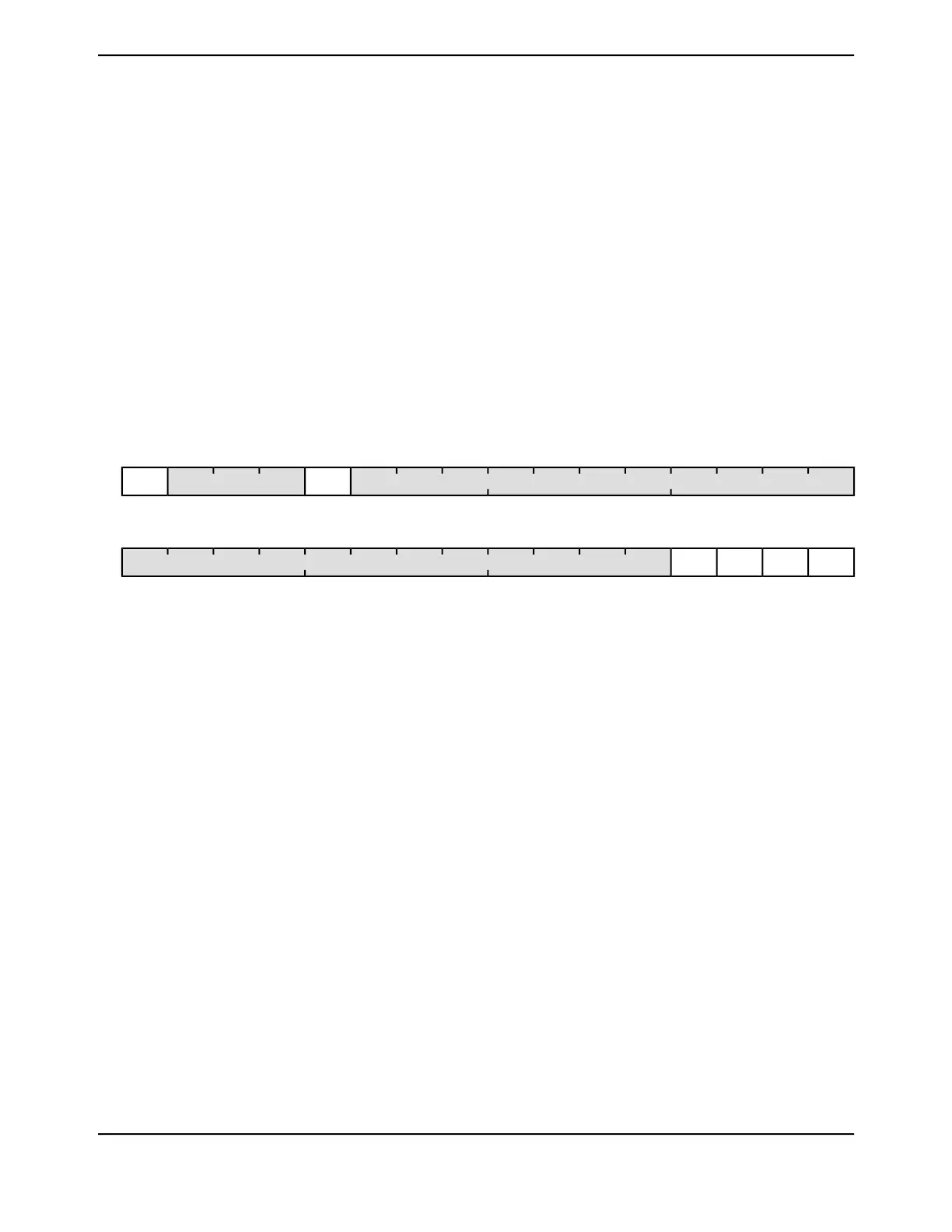

0123456789101112131415

SS0SS1SS2SS3reserved

WOWOWOWOROROROROROROROROROROROROType

----000000000000Reset

DescriptionResetTypeNameBit/Field

Global Synchronize

DescriptionValue

This bit is cleared once sampling has been initiated.0

This bit initiates sampling in multiple ADC modules at the same

time. Any ADC module that has been initialized by setting an

SSn bit and the SYNCWAIT bit starts sampling once this bit is

written.

1

0RWGSYNC31

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved30:28

Synchronize Wait

DescriptionValue

Sampling begins when a sample sequence has been initiated.0

This bit allows the sample sequences to be initiated, but delays

sampling until the GSYNC bit is set.

1

0RWSYNCWAIT27

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.0ROreserved26:4

1103June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...