Register 40: EPI Host-Bus 8 Timing Extension (EPIHB8TIME2), offset 0x314

Important: The MODE field in the EPICFG register determines which configuration is enabled.

For EPIHB8TIME2 to be valid, the MODE field must be 0x2.

EPI Host-Bus 8 Timing Extension (EPIHB8TIME2)

Base 0x400D.0000

Offset 0x314

Type RW, reset 0x0002.2000

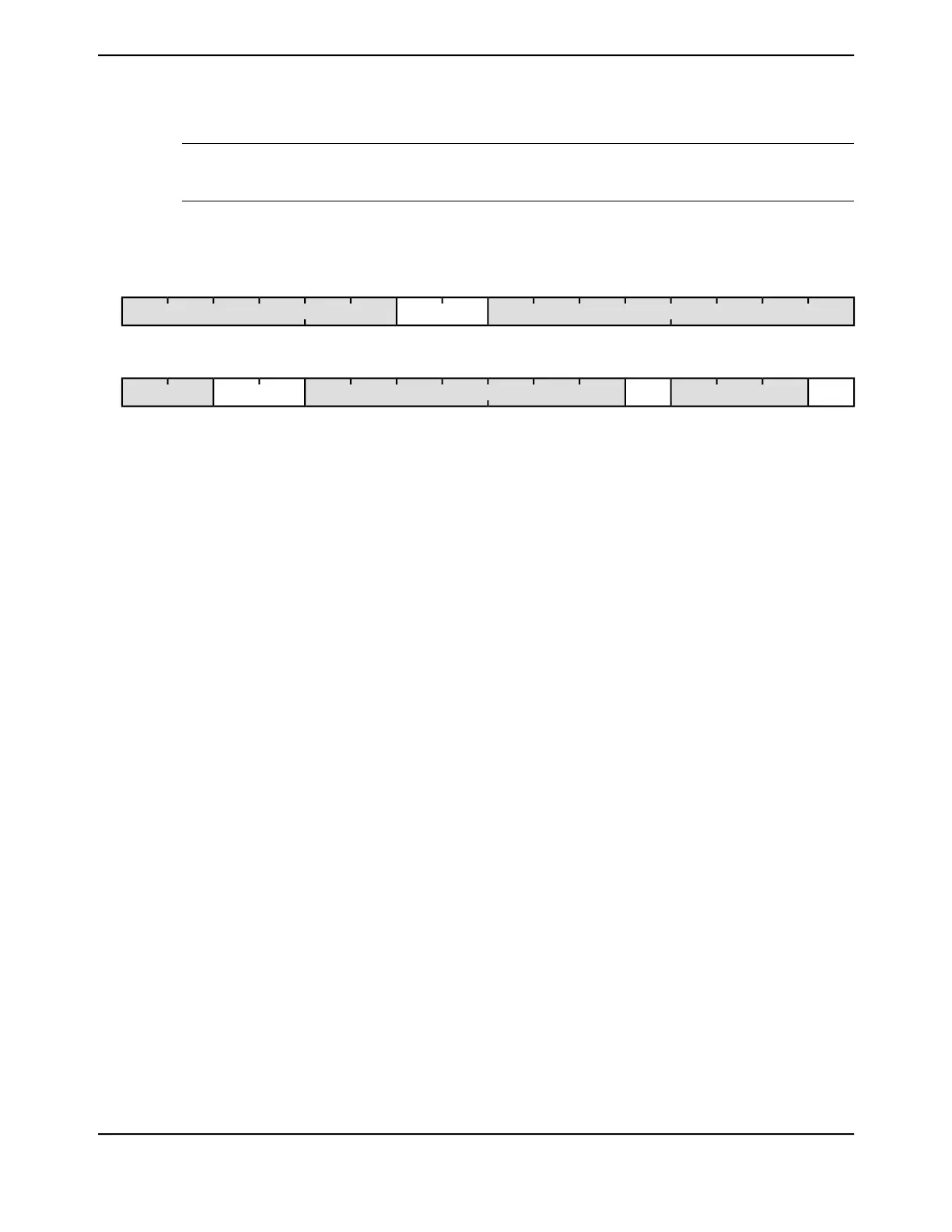

16171819202122232425262728293031

reservedIRDYDLYreserved

RORORORORORORORORWRWROROROROROROType

0000000000000000Reset

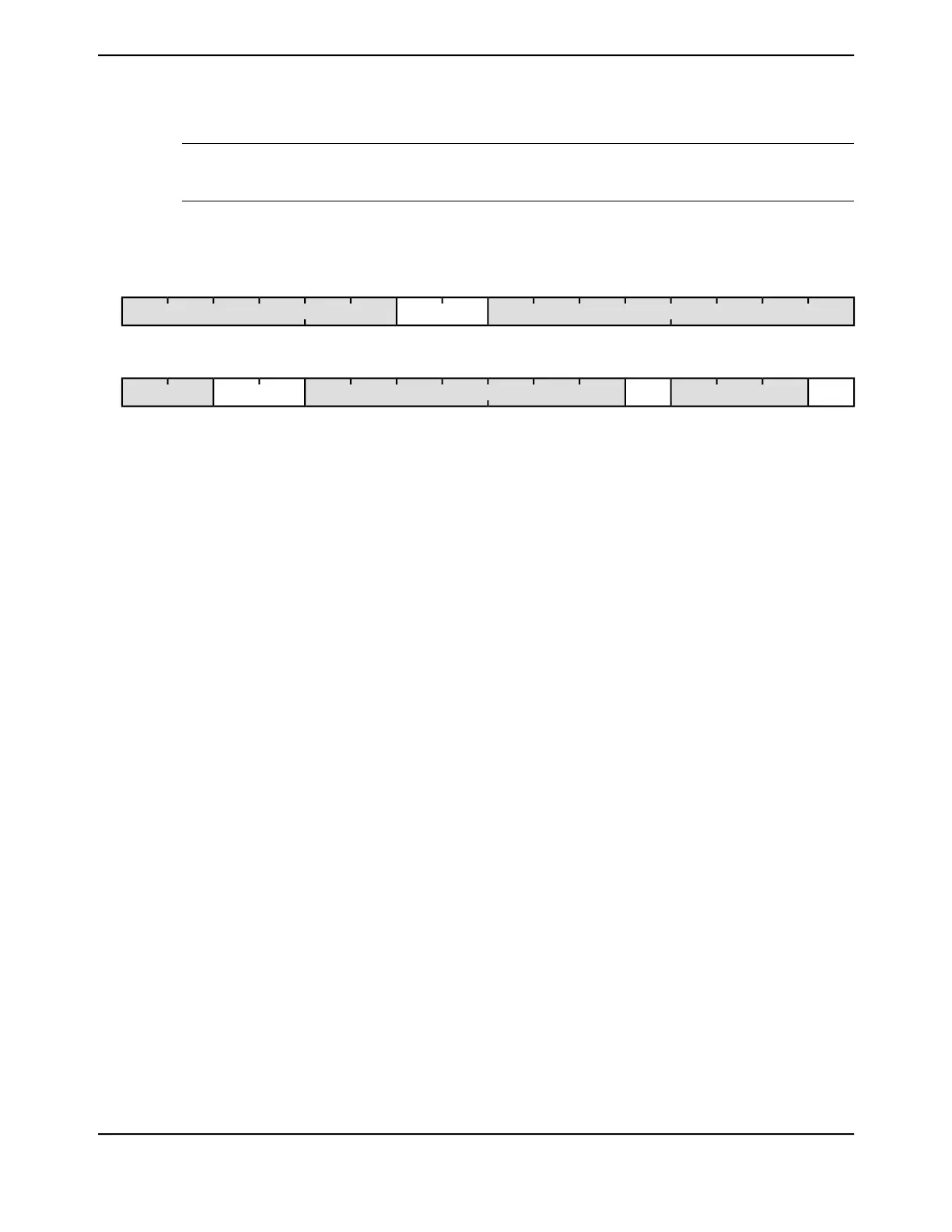

0123456789101112131415

RDWSMreservedWRWSMreservedCAPWIDTHreserved

RWRORORORWRORORORORORORORWRWROROType

0000000000000101Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x00ROreserved31:26

CS1n Input Ready Delay

DescriptionValue

reserved0

Stall begins one EPI clocks past iRDY low being sampled on

the rising edge of EPIO clock.

1

Stall begins two EPI clocks past iRDY low being sampled on

the rising edge of EPIO clock.

2

Stall begins three EPI clocks past iRDY low being sampled on

the rising edge of EPIO clock.

3

0x0RWIRDYDLY25:24

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x002ROreserved23:14

CS1n Inter-transfer Capture Width

Controls the delay between Host-Bus transfers.

DescriptionValue

Reserved0x0

1 EPI clock.0x1

2 EPI clock.0x2

Reserved0x3

0x2RWCAPWIDTH13:12

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x00ROreserved11:5

933June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...