Register 65: ADC Peripheral Configuration (ADCPC), offset 0xFC4

The ADCPC register provides information regarding the configuration of the peripheral.

ADC Peripheral Configuration (ADCPC)

ADC0 base: 0x4003.8000

ADC1 base: 0x4003.9000

Offset 0xFC4

Type RW, reset 0x0000.0007

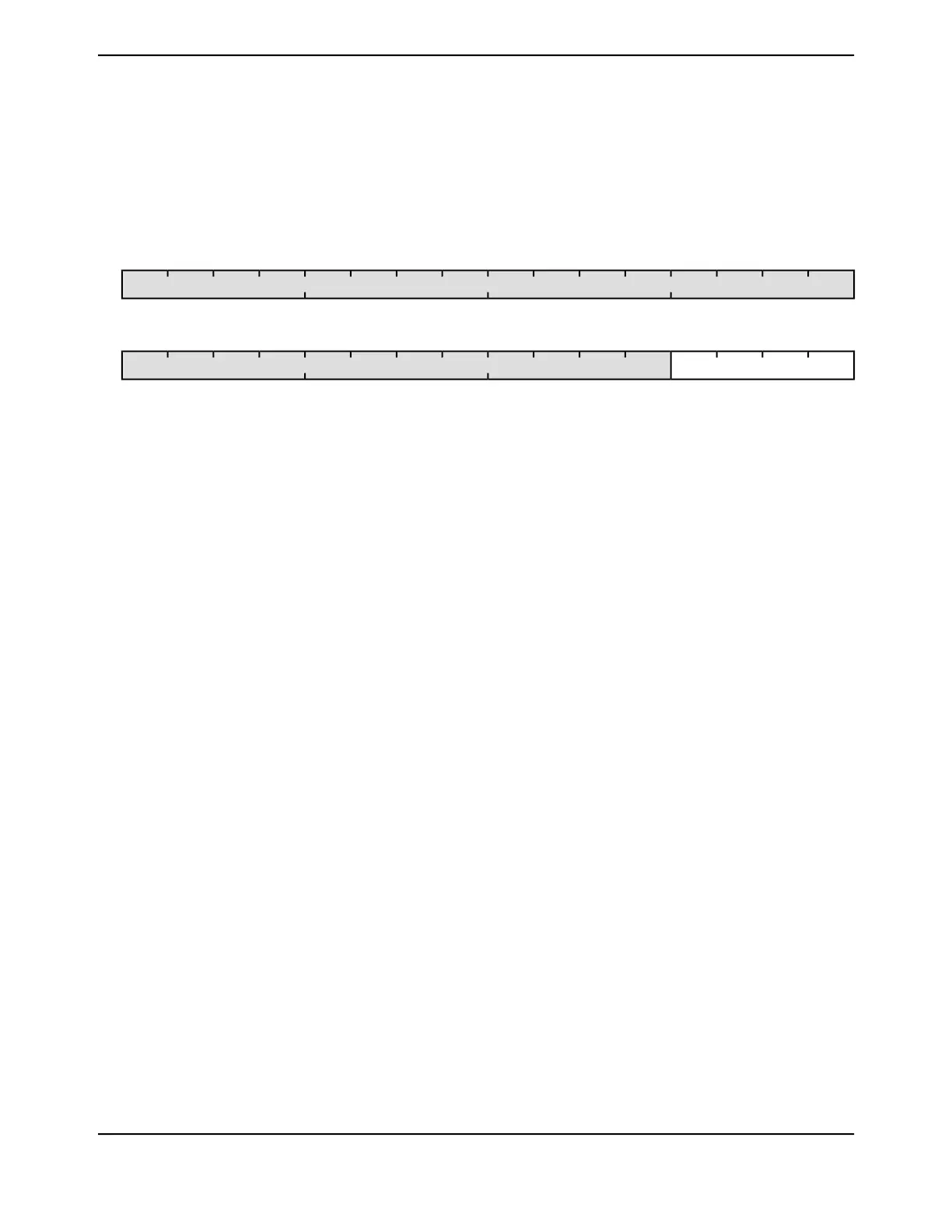

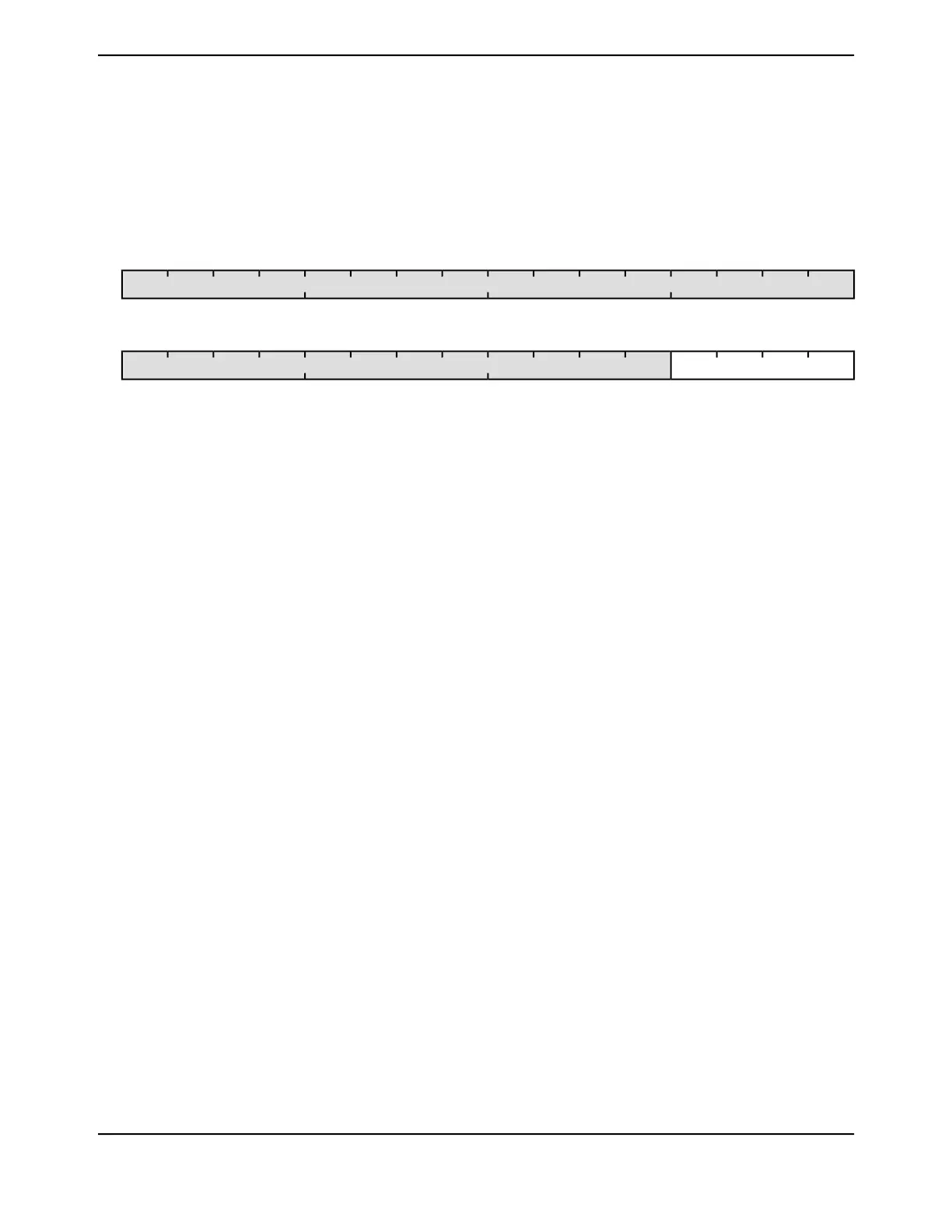

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

0123456789101112131415

MCRreserved

RWRWRWRWROROROROROROROROROROROROType

1110000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.0000ROreserved31:4

Conversion Rate

This field specifies the relative sample rate of the ADC and is used in

run, sleep, and deep-sleep modes. It allows the application to reduce

the rate at which conversions are generated relative to the maximum

conversion rate.

DescriptionValue

Reserved0x0

Eighth conversion rate. After a conversion completes, the

logic pauses for 112 T

ADC

periods before starting the next

conversion.

0x1

Reserved0x2

Quarter conversion rate. After a conversion completes, the

logic pauses for 48 T

ADC

periods before starting the next

conversion.

0x3

Reserved0x4

Half conversion rate. After a conversion completes, the logic

pauses for 16 T

ADC

periods before starting the next

conversion.

0x5

Reserved0x6

Full conversion rate (F

CONV

) as defined by T

ADC

and N

SH

.0x7

Reserved0x8 - 0xF

0x7RWMCR3:0

1159June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...