Revision History

The revision history table notes changes made between the indicated revisions of the

TM4C1294NCPDT data sheet.

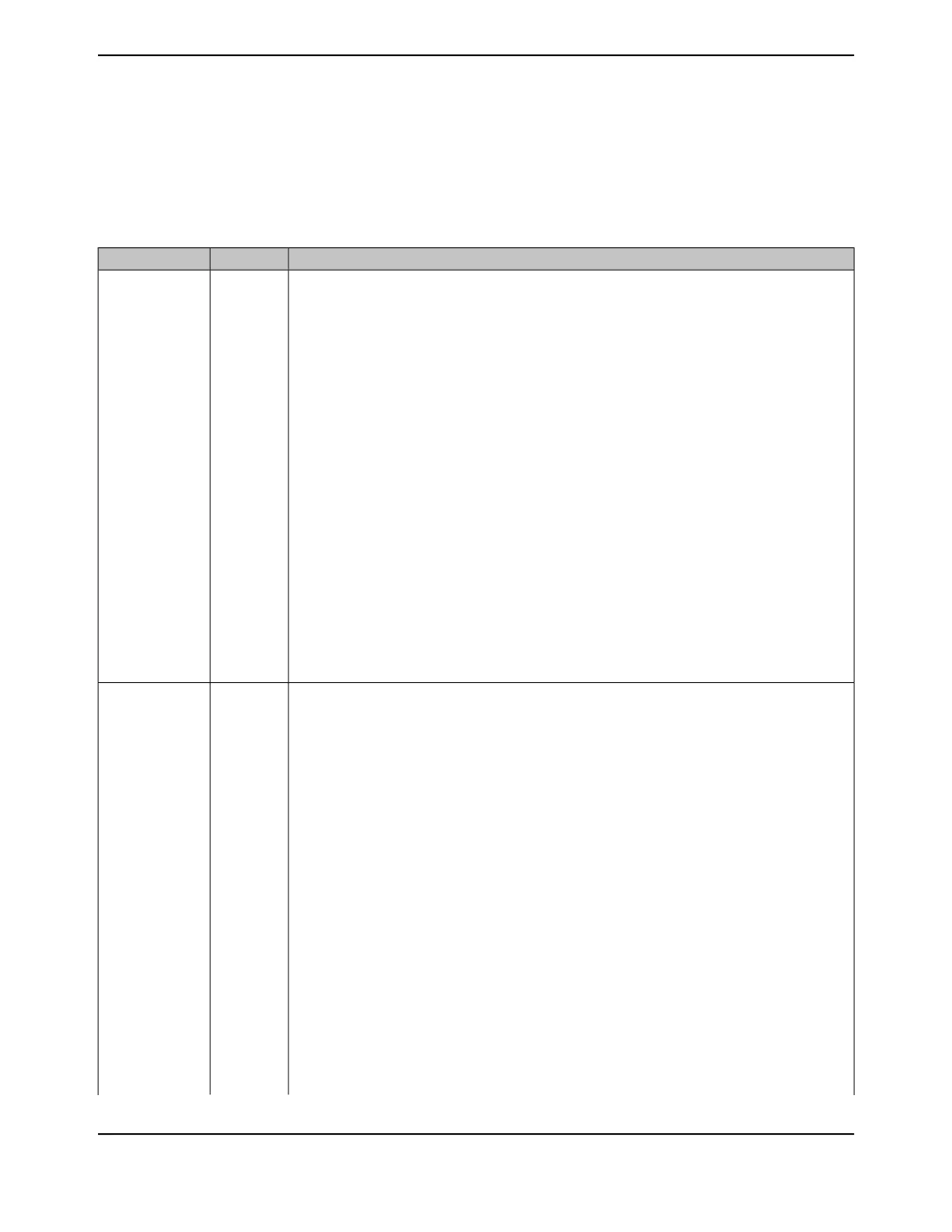

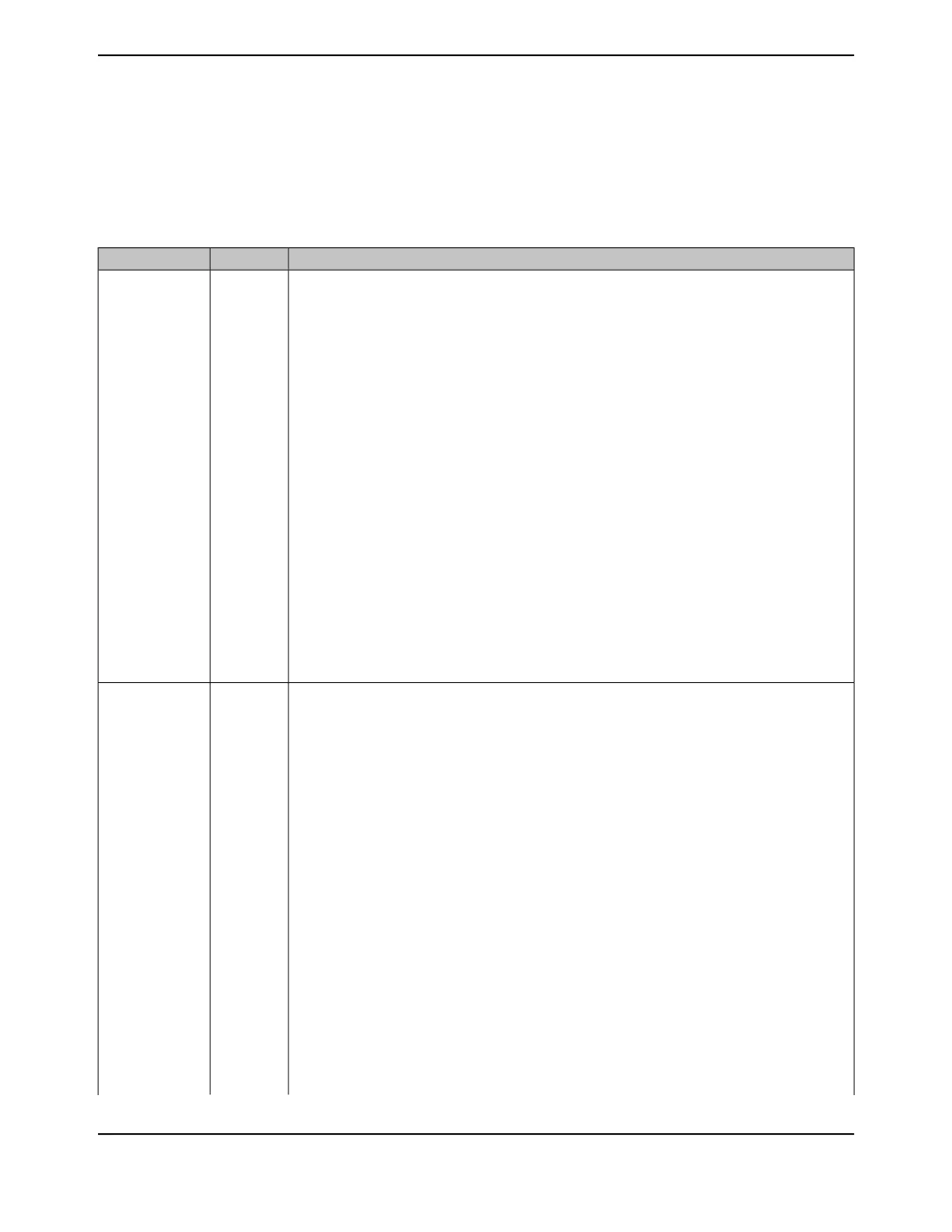

Table 1. Revision History

DescriptionRevisionDate

15863.2743June 2014 ■ In ADC chapter, clarified section "Sample and Hold Window Control".

■ In SSI chapter:

Noted that during idle periods the transmit data line SSInTx is tristated.–

– Added clarification to uDMA section about wait states.

■ In Ethernet chapter:

Corrected functional description of DMA descriptors.–

– Added description of Receive Checksum Offload Engine.

■ In Electrical Characteristics chapter:

In "Power and Brown-Out Levels" table, updated V

POR

with characterized values.–

– In "PIOSC Clock Characteristics" table, clarified F

PIOSC

values.

– In "Low-Frequency Internal Oscillator Characteristics" table, updated F

LFIOSC

with characterized

values.

– In "Main Oscillator Input Characteristics" table, removed Pending Characterization footnote.

– In "ADC Electrical Characteristics for ADC at 1 Msps" table, updated Max value for VIN

CM

.

– In "ADC Electrical Characteristics for ADC at 2 Msps" table, updated values for VIN

CM

, R

S

,

f

CONV

, T

S

, T

LT

, and the Dynamic Characteristics.

– In "Current Consumption" table, updated values that were pending.

■ In Package Information appendix:

Moved Orderable Part Numbers table to addendum.–

– Deleted Packaging Materials section and put into separate packaging document.

■ Additional minor data sheet clarifications and corrections.

15802.2729April 2014 ■ In the System Control chapter:

Clarified Hibernation Module reset section.–

– Added clarifications in Deep-Sleep Mode section.

– Added reset for DID1 register.

– Corrected description for RESC register, and changed bit 6 HIB Reset to reserved.

– Added note to DSSYSDIV bit in DSCLKCFG register that values 0x0 and 0x1 should not be

used.

– Added clarification to FLASHPM bit in DSLPPWRCFG register when using the LFIOSC as the

Deep-Sleep clock source.

– Added four registers, UNIQUEIDn, which combined provide a 128-bit unique identifier for each

device.

■ In the Hibernation chapter, added clarification to Hibernation Control (HIBCTL) register about

External Wake and Interrupt Pin Enable bit.

■ In the Internal Memory chapter, added information on soft reset handling to the EEPROM section.

■ In the GPIO chapter:

Replaced table GPIO Pins With Non-Zero Reset Values with table GPIO Pins With Special

Considerations.

–

– Added note about preventing false interrupts.

■ In the Timer chapter, clarified behavior of TnMIE and TnCINTD bits in the GPTM Timer n Mode

(GPTMTnMR) registers.

■ In the ADC chapter:

Corrected ADC maximum sample rate to two million samples/second.–

45June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...