Register 82: Ethernet PHY Configuration 2 - MR10 (EPHYCFG2), address

0x00A

Fields in this register are used to configure the Ethernet PHY. These configuration values are

programmed by the system processor after a POR. The DONE bit in the EPHYCFG1 register is set

when configuration is complete. This register is used when the user requires a configuration different

from what is provided in the EMACPC register.

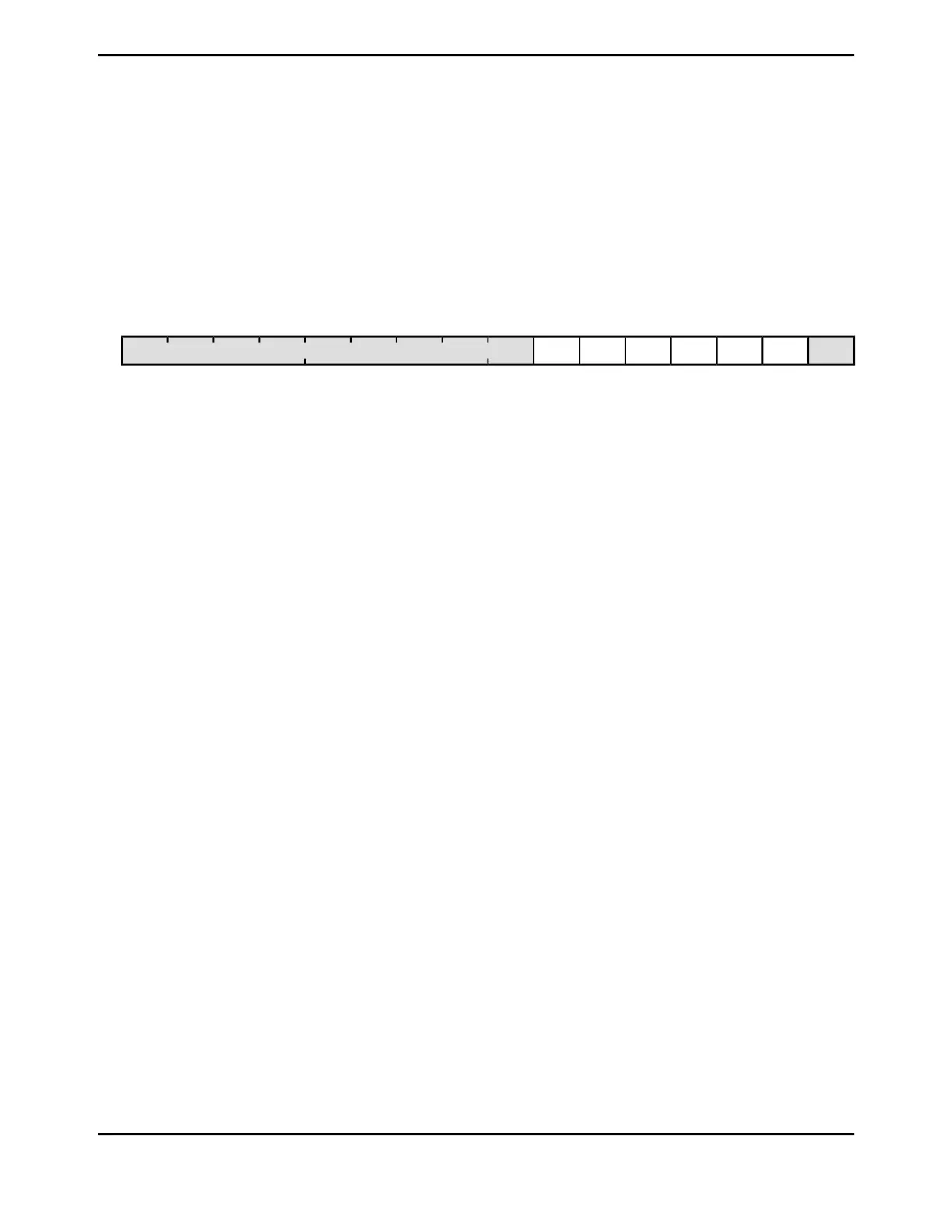

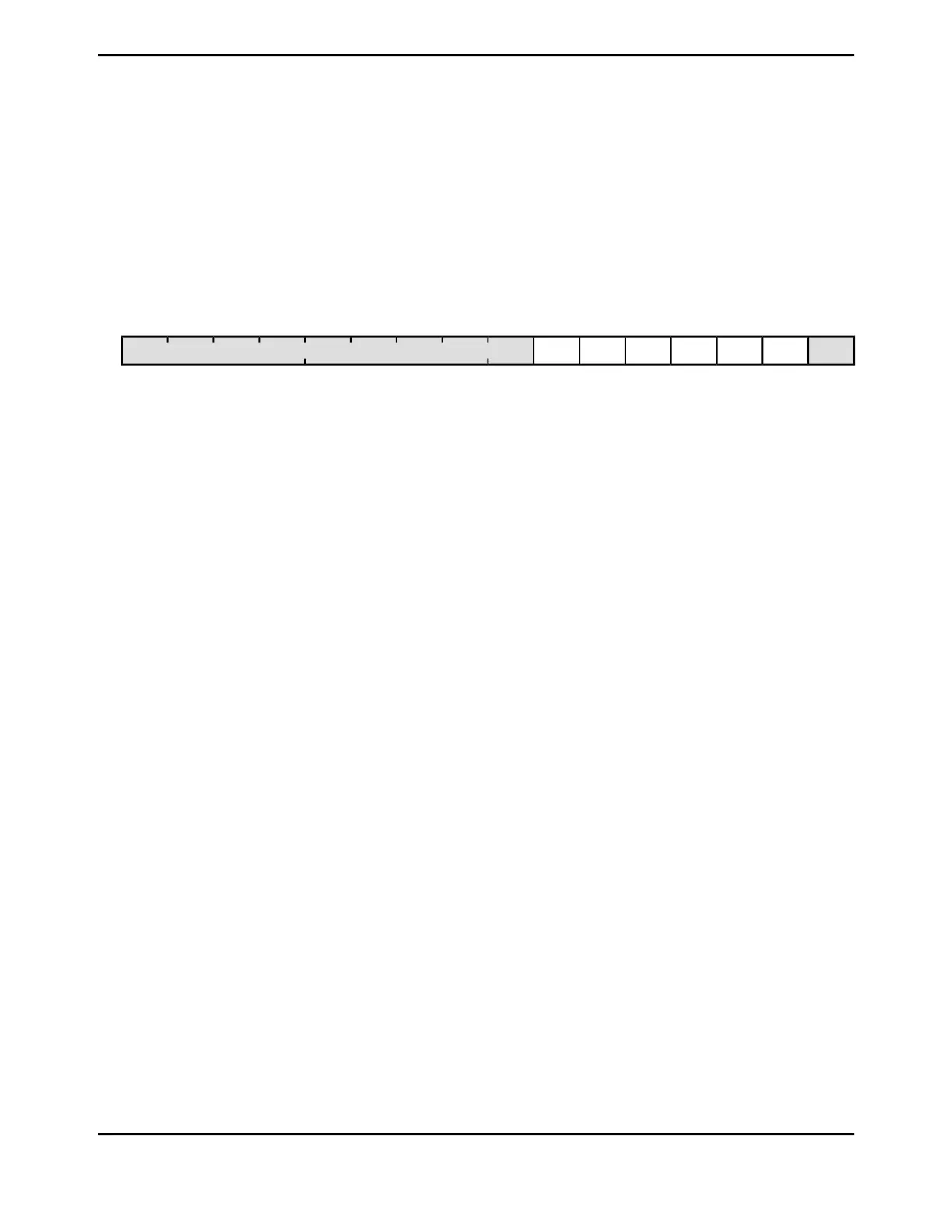

Ethernet PHY Configuration 2 - MR10 (EPHYCFG2)

Base n/a

Address 0x00A

Type RW, reset 0x0004

0123456789101112131415

reserved

ODDNDETDISRXERRIDLE

ISOMIILL

ENLEDLINK

EXTFDFLUPPDreserved

RORWRWRWRWRWRWROROROROROROROROROType

0010000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved15:7

Fast Link-Up in Parallel Detect Mode

In fast-auto MDI-X and in robust-auto MDI-X modes (bits 6 and 5 in

register EPHYCFG1), this bit is automatically set.

DescriptionValue

Normal Parallel Detection link establishment0

Enable Fast Link-Up time During Parallel Detection1

0x0RWFLUPPD6

Extended Full-Duplex Ability

Encodes the type of PHY attached.

DescriptionValue

Disable extended full-duplex ability. Decision to work in

full-duplex or half-duplex mode follows IEEE specification.

0

Force full-duplex while working with link partner in forced

100B-TX. When the PHY is set to Auto-Negotiation or Force

100B-TX and the link partner is operated in Force 100B-TX, the

link is always full duplex

1

0RWEXTFD5

Enhanced LED Functionality

DescriptionValue

LED Link is ON when link is established.0

LED Link is ON only when link is established in 100B-TX Full

Duplex mode.

1

0RWENLEDLINK4

1609June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...