Register 3: DMA Channel Control Word (DMACHCTL), offset 0x008

DMA Channel Control Word (DMACHCTL) is part of the Channel Control Structure and is used

to specify parameters of a μDMA transfer.

Note: The offset specified is from the base address of the control structure in system memory,

not the μDMA module base address.

DMA Channel Control Word (DMACHCTL)

Base n/a

Offset 0x008

Type RW, reset -

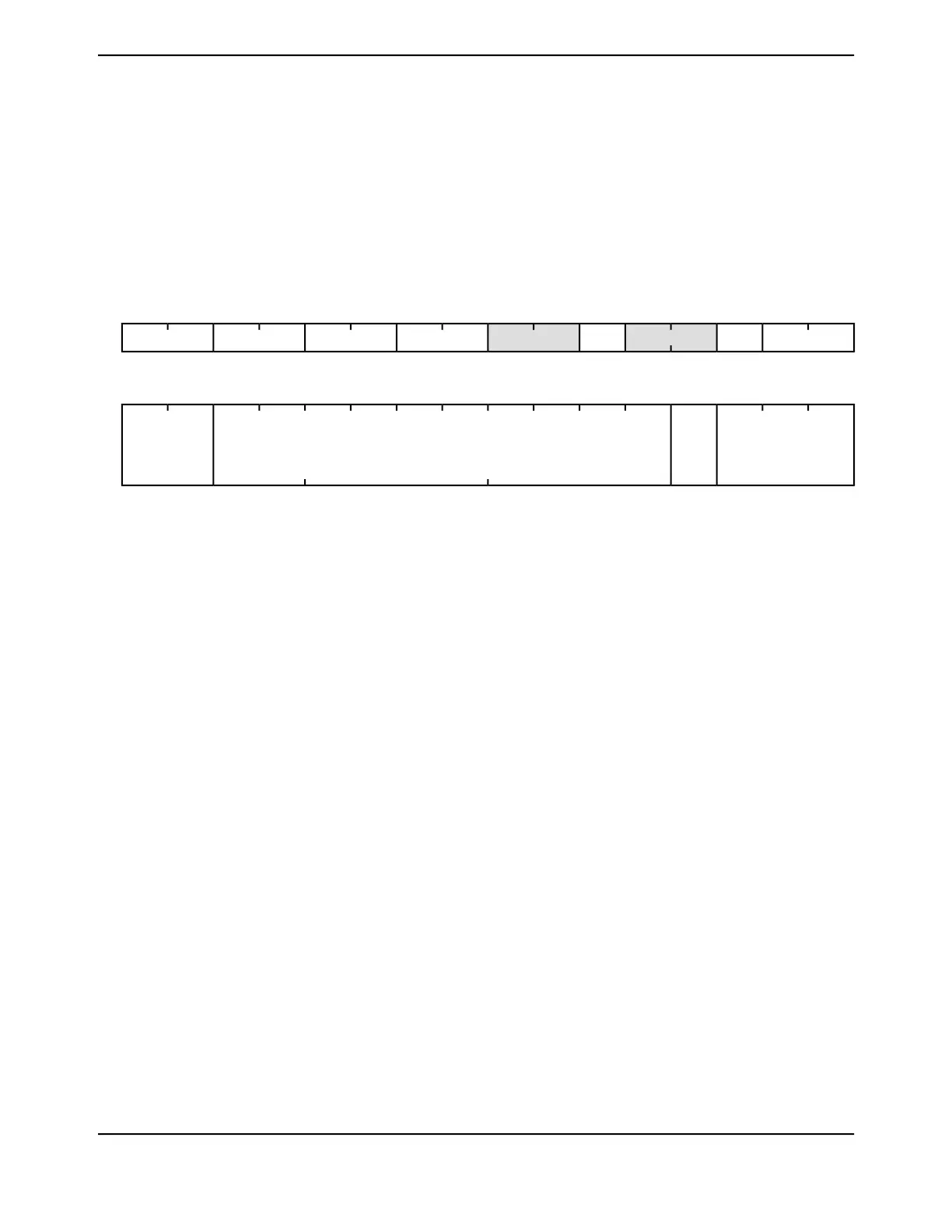

16171819202122232425262728293031

ARBSIZE

SRCPROT0

reserved

DSTPROT0

reservedSRCSIZESRCINCDSTSIZEDSTINC

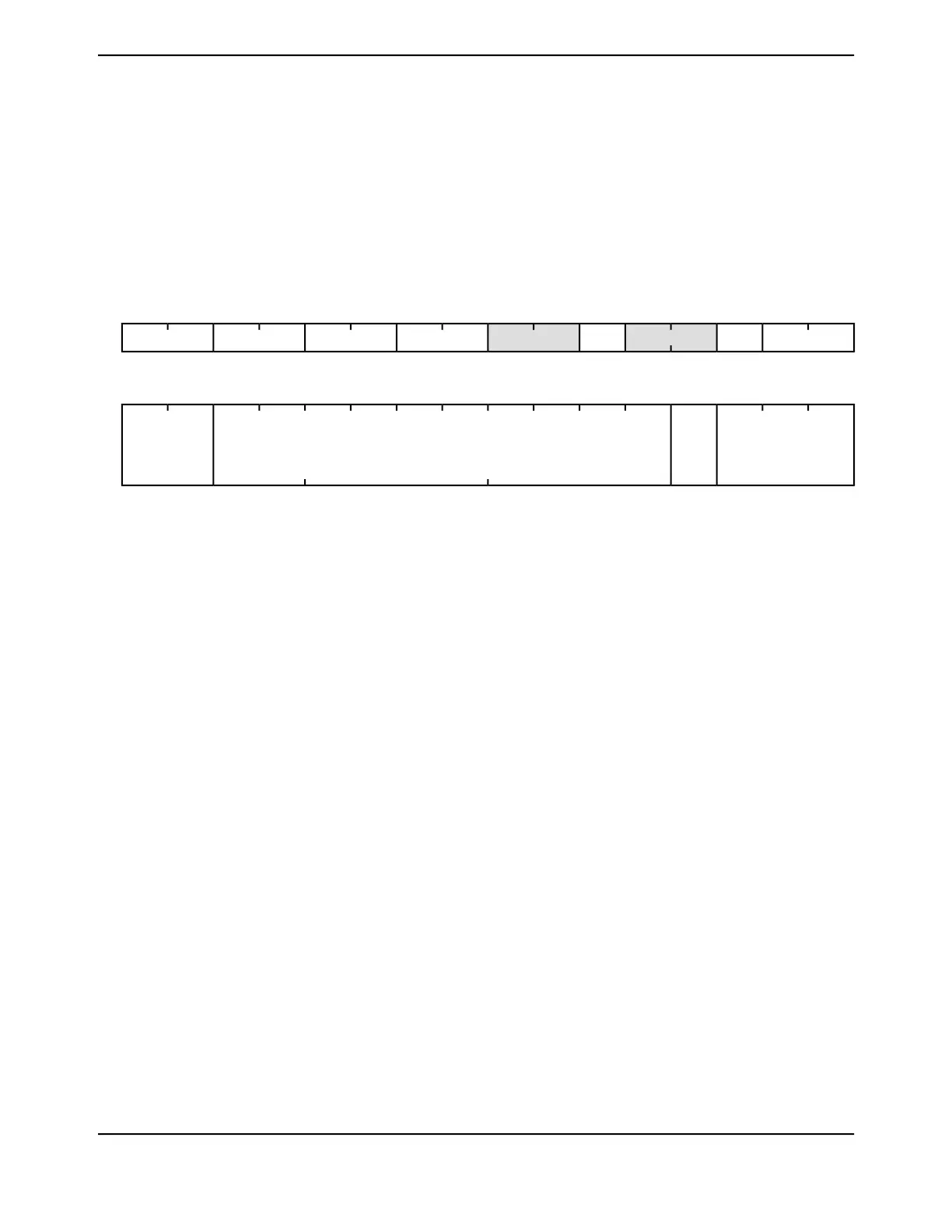

RWRWRWRORORWRORORWRWRWRWRWRWRWRWType

--0--000--------Reset

0123456789101112131415

XFERMODE

NXTUSEBURST

XFERSIZEARBSIZE

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWRWType

----------------Reset

DescriptionResetTypeNameBit/Field

Destination Address Increment

This field configures the destination address increment.

The address increment value must be equal or greater than the value

of the destination size (DSTSIZE).

DescriptionValue

Byte

Increment by 8-bit locations

0x0

Half-word

Increment by 16-bit locations

0x1

Word

Increment by 32-bit locations

0x2

No increment

Address remains set to the value of the Destination Address

End Pointer (DMADSTENDP) for the channel

0x3

-RWDSTINC31:30

705June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...