Register 4: EPI SDRAM Configuration (EPISDRAMCFG), offset 0x010

Important: The MODE field in the EPICFG register determines which configuration register is

accessed for offsets 0x010 and 0x014.

To access EPISDRAMCFG, the MODE field must be 0x1.

The SDRAM Configuration register is used to specify several parameters for the SDRAM controller.

Note that this register is reset when the MODE field in the EPICFG register is changed. If another

mode is selected and the SDRAM mode is selected again, the values must be reinitialized.

The SDRAM interface is designed to interface to x16 SDR SDRAMs of 64 MHz or higher, with the

address and data pins overlapped (wire ORed on the board). See Table 11-3 on page 823 for pin

assignments.

EPI SDRAM Configuration (EPISDRAMCFG)

Base 0x400D.0000

Offset 0x010

Type RW, reset 0x82EE.0000

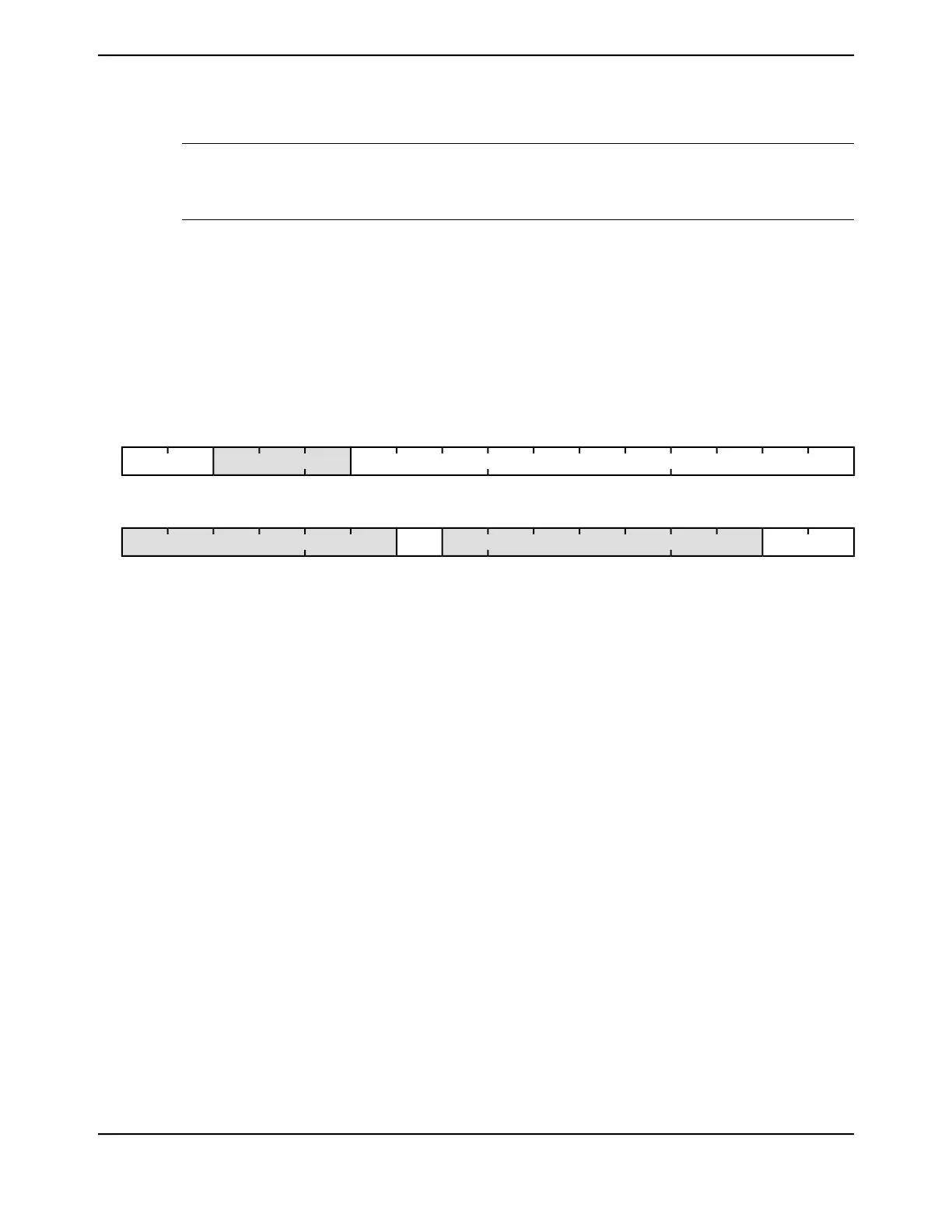

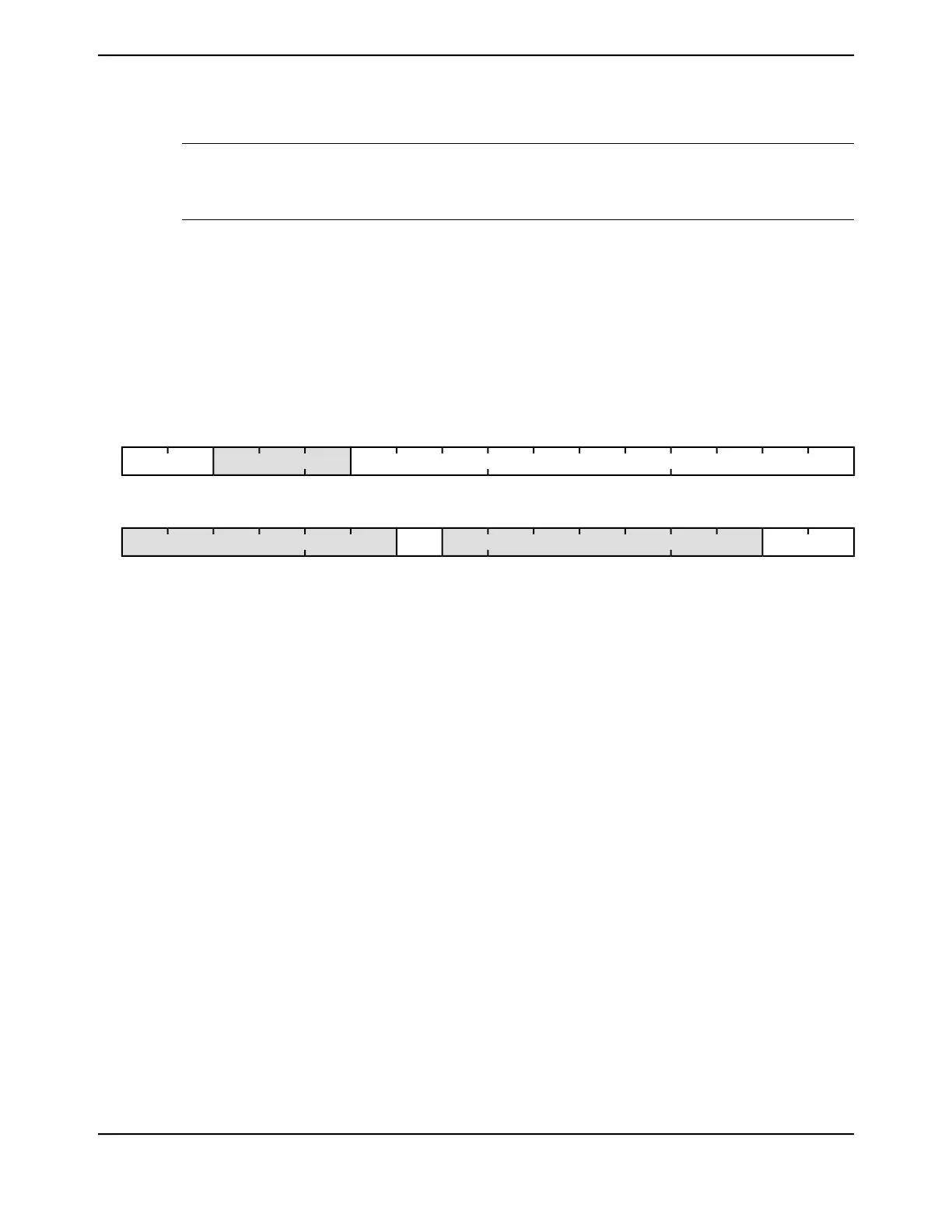

16171819202122232425262728293031

RFSHreservedFREQ

RWRWRWRWRWRWRWRWRWRWRWRORORORWRWType

0111011101000001Reset

0123456789101112131415

SIZEreservedSLEEPreserved

RWRWRORORORORORORORWROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

EPI Frequency Range

This field configures the frequency range used for delay references by

internal counters. This EPI frequency is the system frequency with the

divider programmed by the COUNT0 bit in the EPIBAUDn register bit.

This field affects the power up, precharge, and auto refresh delays. This

field does not affect the refresh counting, which is configured separately

using the RFSH field (and is based on system clock rate and number of

rows per bank). The ranges are:

DescriptionValue

0 - 15 MHz0x0

15 - 30 MHz0x1

30 - 50 MHz0x2

50 - 100 MHz0x3

0x2RWFREQ31:30

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved29:27

Refresh Counter

This field contains the refresh counter in EPI clocks. The reset value of

0x2EE provides a refresh period of 64 ms when using a 50 MHz EPI

clock.

0x2EERWRFSH26:16

863June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...