Register 4: DMA Status (DMASTAT), offset 0x000

The DMA Status (DMASTAT) register returns the status of the μDMA controller. You cannot read

this register when the μDMA controller is in the reset state.

DMA Status (DMASTAT)

Base 0x400F.F000

Offset 0x000

Type RO, reset 0x001F.0000

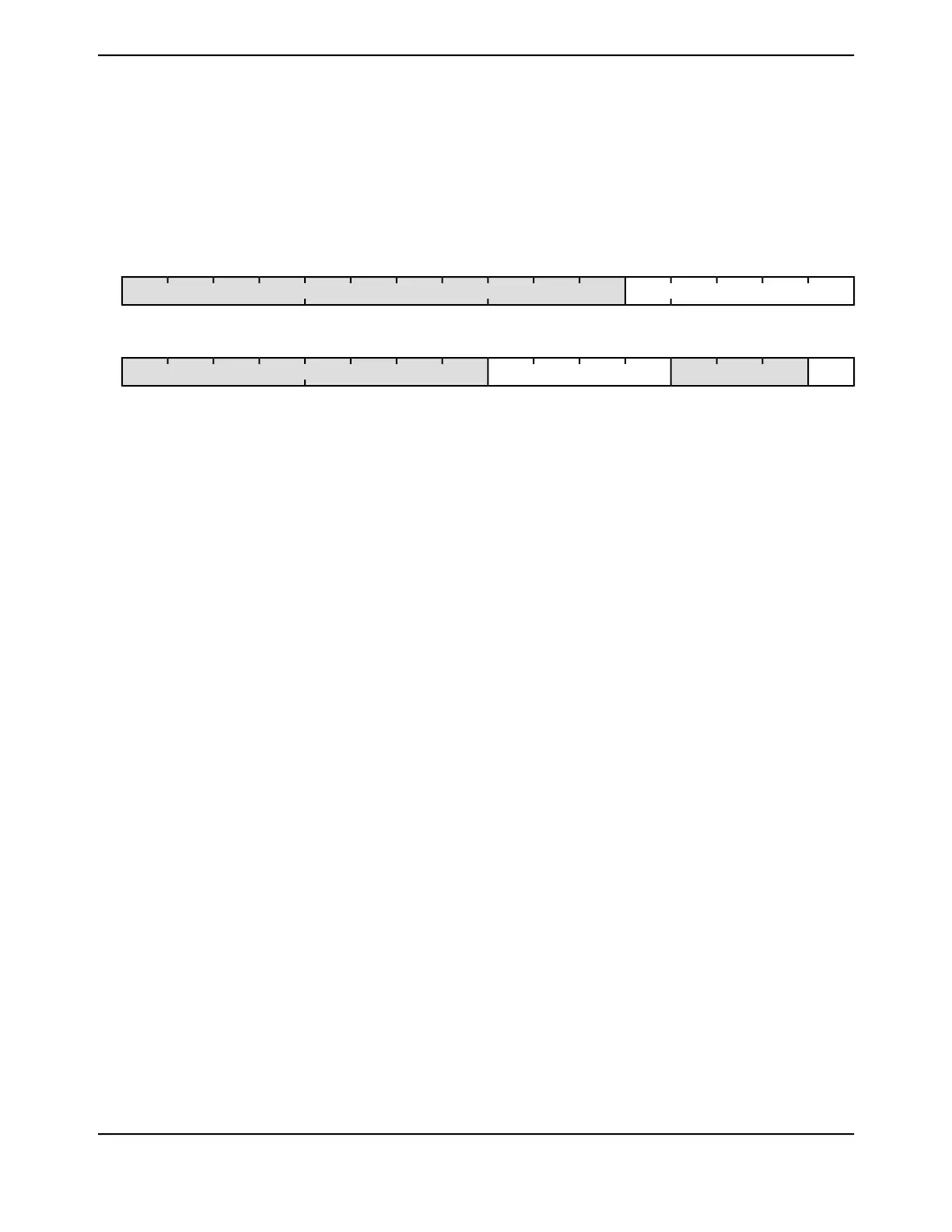

16171819202122232425262728293031

DMACHANSreserved

ROROROROROROROROROROROROROROROROType

1111100000000000Reset

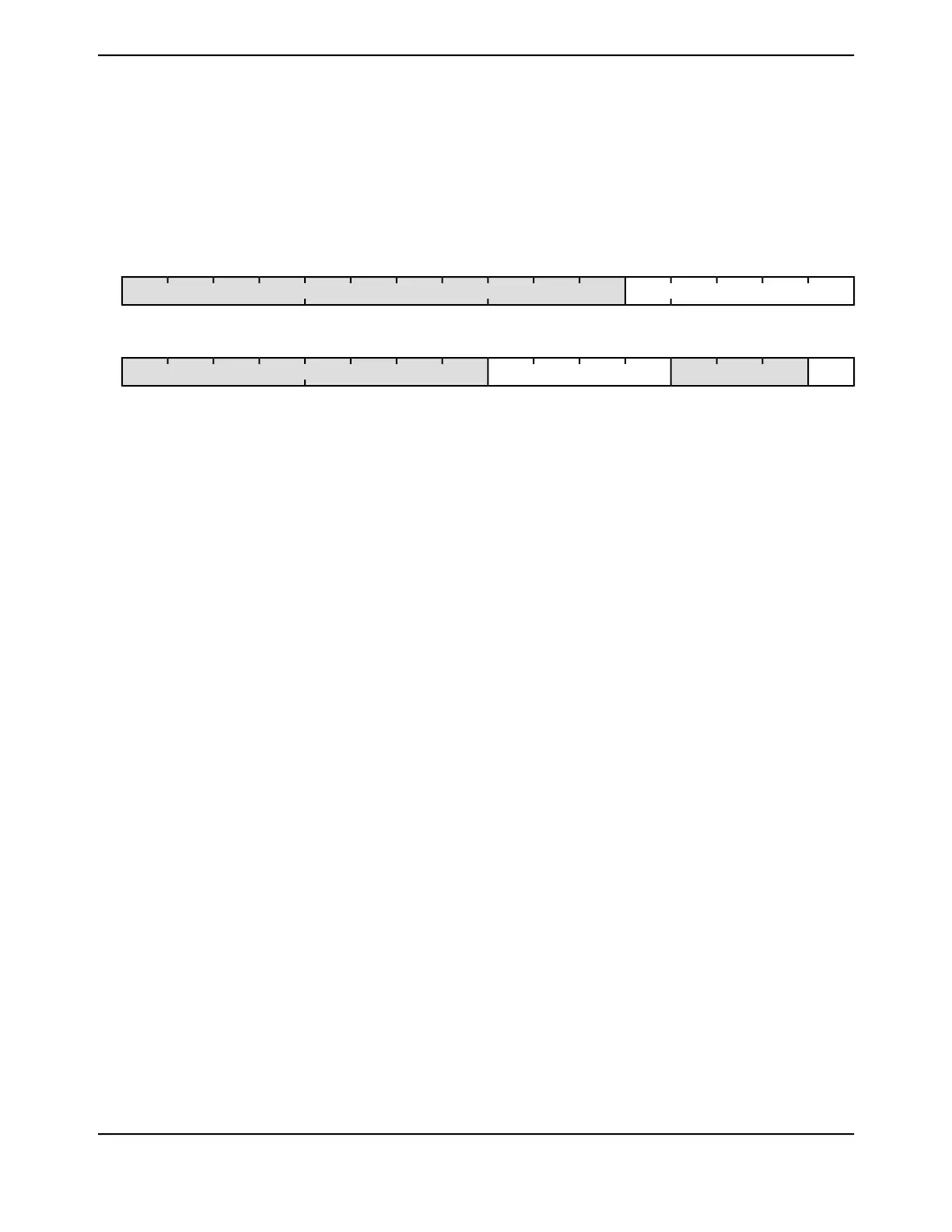

0123456789101112131415

MASTENreservedSTATEreserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x000ROreserved31:21

Available μDMA Channels Minus 1

This field contains a value equal to the number of μDMA channels the

μDMA controller is configured to use, minus one. The value of 0x1F

corresponds to 32 μDMA channels.

0x1FRODMACHANS20:16

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x00ROreserved15:8

Control State Machine Status

This field shows the current status of the control state machine. Status

can be one of the following.

DescriptionValue

Idle0x0

Reading channel controller data.0x1

Reading source end pointer.0x2

Reading destination end pointer.0x3

Reading source data.0x4

Writing destination data.0x5

Waiting for µDMA request to clear.0x6

Writing channel controller data.0x7

Stalled0x8

Done0x9

Undefined0xA-0xF

0x0ROSTATE7:4

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved3:1

June 18, 2014710

Texas Instruments-Production Data

Micro Direct Memory Access (μDMA)

Loading...

Loading...