Register 7: Hibernation Masked Interrupt Status (HIBMIS), offset 0x01C

This register is the masked interrupt status for the Hibernation module interrupt sources. Bits in this

register are the AND of the corresponding bits in the HIBRIS and HIBIM registers. When both

corresponding bits are set, the bit in this register is set, and the interrupt is sent to the interrupt

controller.

Hibernation Masked Interrupt Status (HIBMIS)

Base 0x400F.C000

Offset 0x01C

Type RO, reset 0x0000.0000

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

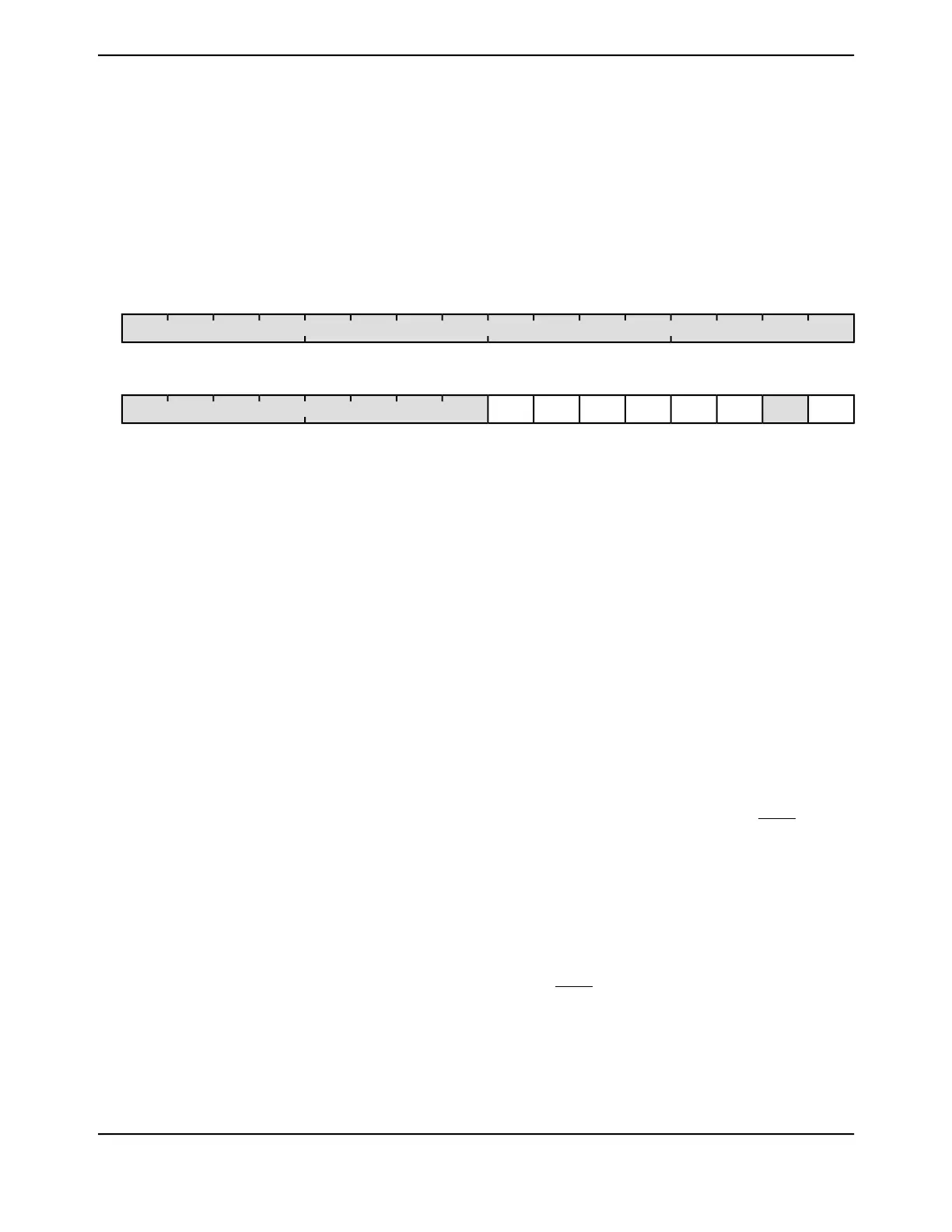

0123456789101112131415

RTCALT0reservedLOWBATEXTWWCPADIOWKRSTWKVDDFAILreserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.000ROreserved31:8

VDD Fail Interrupt Mask

DescriptionValue

An VDDFAIL interrupt has not occurred or is masked.0

An unmasked interrupt was signaled due to a an arbitrary loss

of power or because on or more of the voltage supplies (VDD,

VDDA or VDDC) has dropped below the defined operating

range.

1

0ROVDDFAIL7

Reset Pad I/O Wake-Up Interrupt Mask

DescriptionValue

An external reset interrupt has not occurred or is masked.0

An unmasked interrupt was signaled due to a RESET pin

assertion.

1

0RORSTWK6

Pad I/O Wake-Up Interrupt Mask

DescriptionValue

An external GPIO or reset interrupt has not occurred or is

masked.

0

An unmasked interrupt was signaled due to a wake-enabled

GPIO or RESET pin assertion.

1

0ROPADIOWK5

June 18, 2014566

Texas Instruments-Production Data

Hibernation Module

Loading...

Loading...