Register 60: Configuration and Control (CFGCTRL), offset 0xD14

Note: This register can only be accessed from privileged mode.

The CFGCTRL register controls entry to Thread mode and enables: the handlers for NMI, hard fault

and faults escalated by the FAULTMASK register to ignore bus faults; trapping of divide by zero

and unaligned accesses; and access to the SWTRIG register by unprivileged software (see page 163).

Configuration and Control (CFGCTRL)

Base 0xE000.E000

Offset 0xD14

Type RW, reset 0x0000.0200

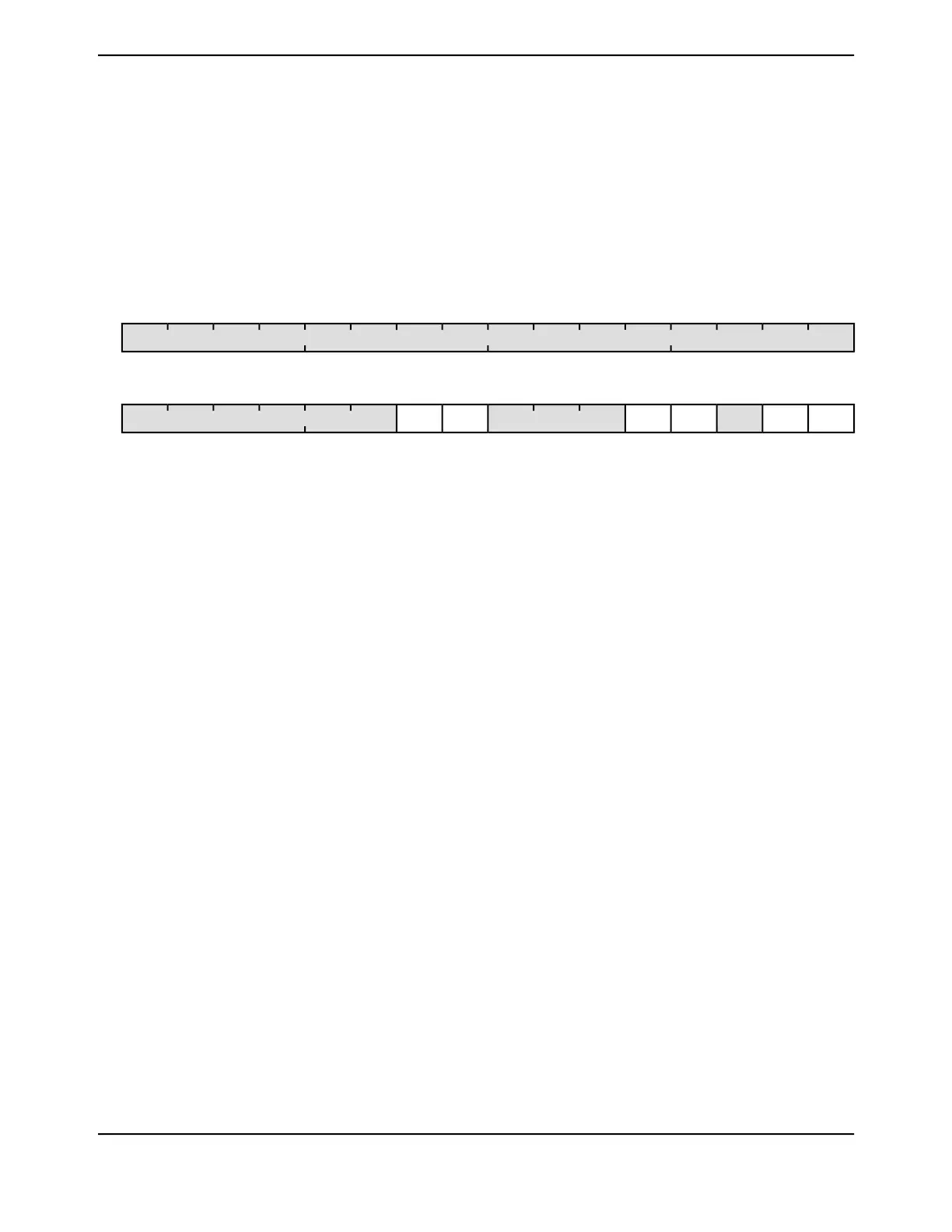

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

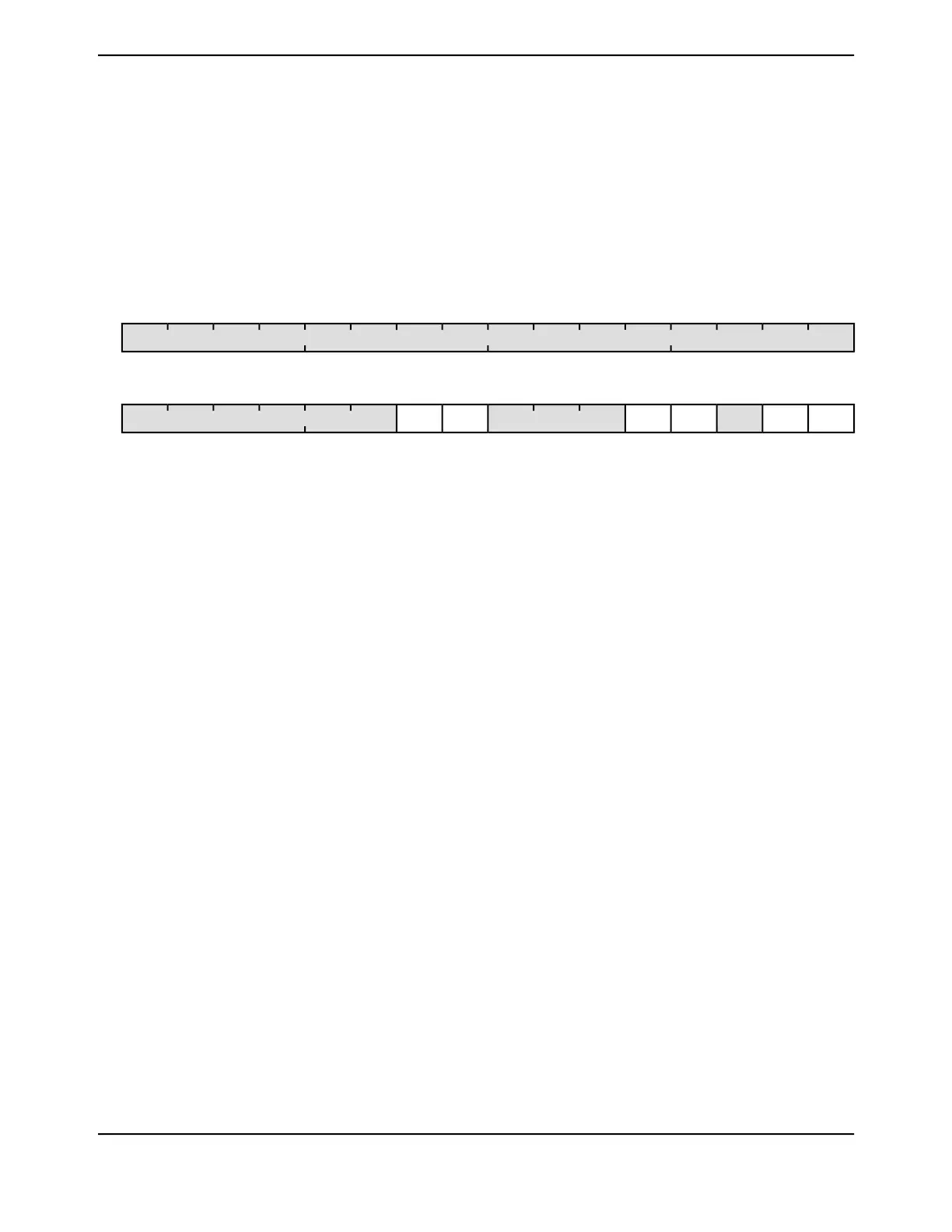

0123456789101112131415

BASETHR

MAINPEND

reserved

UNALIGNED

DIV0reserved

BFHFNMIGN

STKALIGN

reserved

RWRWRORWRWRORORORWRWROROROROROROType

0000000001000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.00ROreserved31:10

Stack Alignment on Exception Entry

DescriptionValue

The stack is 4-byte aligned.0

The stack is 8-byte aligned.1

On exception entry, the processor uses bit 9 of the stacked PSR to

indicate the stack alignment. On return from the exception, it uses this

stacked bit to restore the correct stack alignment.

1RWSTKALIGN9

Ignore Bus Fault in NMI and Fault

This bit enables handlers with priority -1 or -2 to ignore data bus faults

caused by load and store instructions. The setting of this bit applies to

the hard fault, NMI, and FAULTMASK escalated handlers.

DescriptionValue

Data bus faults caused by load and store instructions cause a

lock-up.

0

Handlers running at priority -1 and -2 ignore data bus faults

caused by load and store instructions.

1

Set this bit only when the handler and its data are in absolutely safe

memory. The normal use of this bit is to probe system devices and

bridges to detect control path problems and fix them.

0RWBFHFNMIGN8

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved7:5

175June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...