Register 25: Ethernet MAC MMC Transmit Raw Interrupt Status

(EMACMMCTXRIS), offset 0x108

The MAC MMC Transmit Interrupt (EMACMMCTXRIS) register maintains the interrupts generated

when transmit statistic counters reach half of their maximum values (0x8000_0000 for 32-bit counter

and 0x8000 for 16-bit counter), and the maximum values (0xFFFF_FFFF for 32-bit counter and

0xFFFF for 16-bit counter). When the CNTSTPRO bit is set in the MAC MMC Control

(EMACMMCCTRL) register, interrupts are set but the counter remains at all-ones. The

EMACMMCTXRIS register is a 32-bit wide register. An interrupt bit is cleared when the respective

MMC counter that caused the interrupt is read. The least significant byte lane (Bits[7:0]) of the

respective counter must be read in order to clear the interrupt bit.

Ethernet MAC MMC Transmit Raw Interrupt Status (EMACMMCTXRIS)

Base 0x400E.C000

Offset 0x108

Type R, reset 0x0000.0000

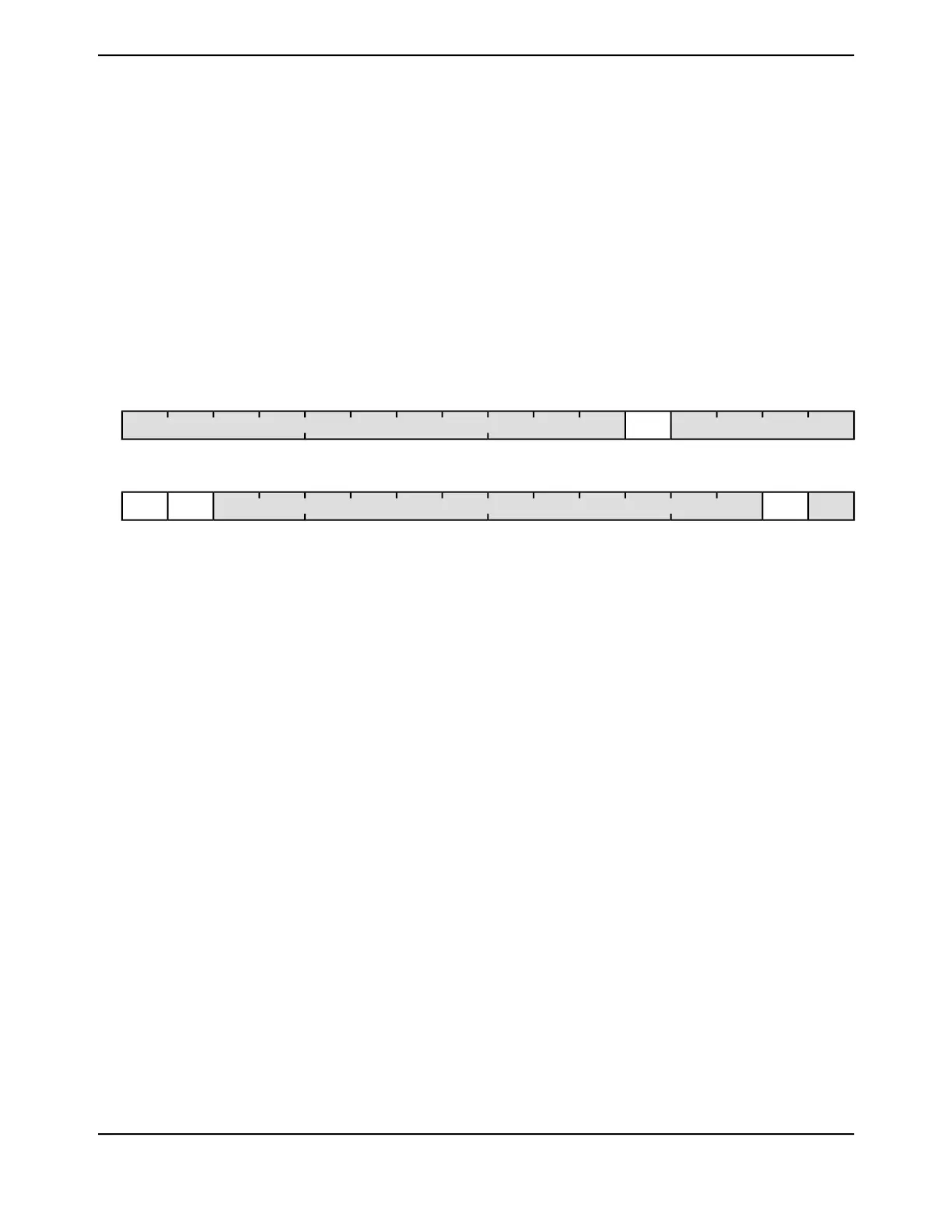

16171819202122232425262728293031

reservedOCTCNTreserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

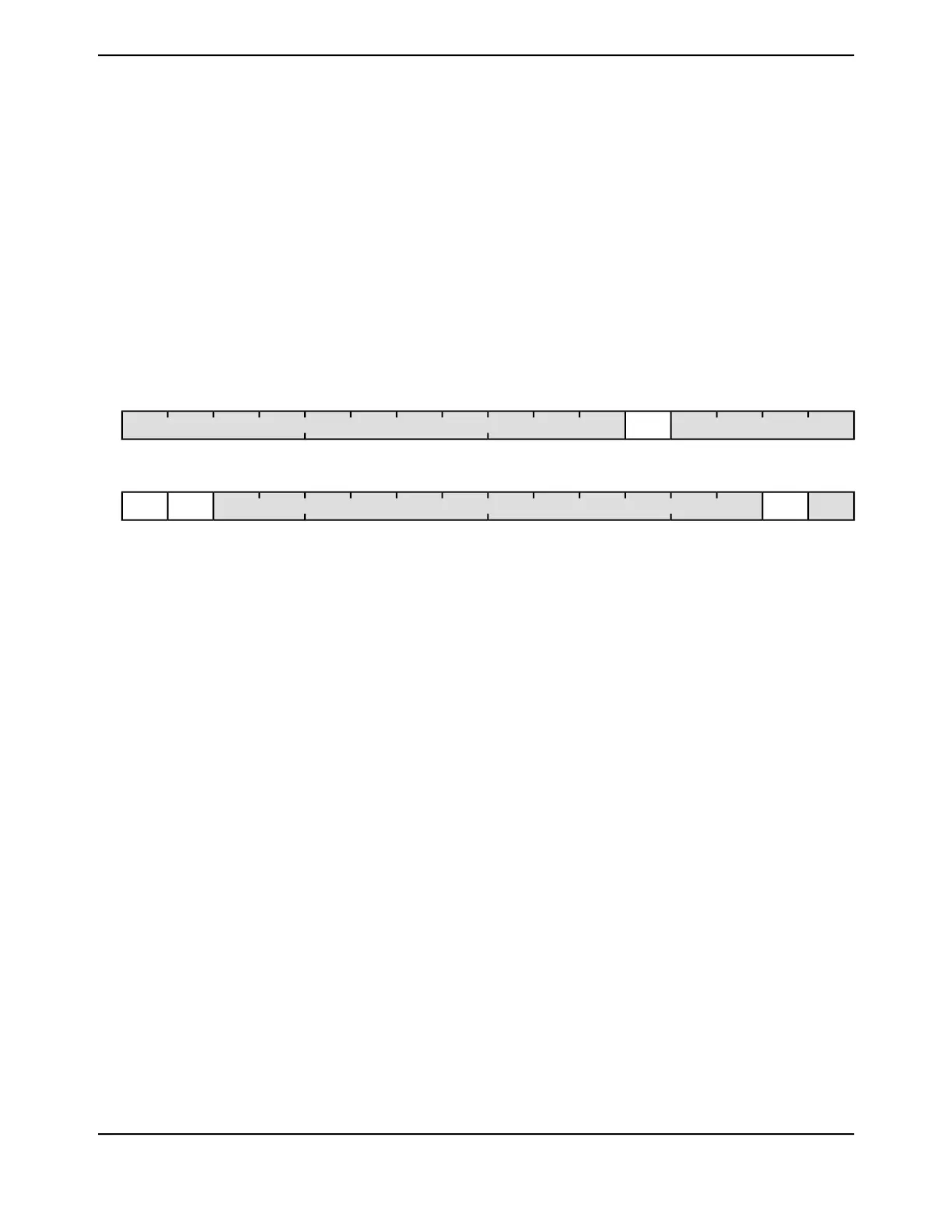

0123456789101112131415

reservedGBFreservedSCOLLGFMCOLLGF

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved31:21

Octet Counter Interrupt Status

DescriptionValue

The Ethernet MAC Transmit Octet Count Good

(EMACTXOCTCNTG) register has not reached half of the

maximum value or the maximum value.

0

The Ethernet MAC Transmit Octet Count Good

(EMACTXOCTCNTG) register has reached half of the maximum

value or the maximum value.

1

0x0ROOCTCNT20

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0ROreserved19:16

1517June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...