Register 7: Ethernet MAC Flow Control (EMACFLOWCTL), offset 0x018

The Ethernet MAC Flow Control (EMACFLOWCTL) register controls the generation and reception

of the control (pause command) frames by the MAC's Flow control module. A write to a register with

the FCBBPA (bit 0) set to 1 triggers the Flow Control block to generate a pause control frame. The

fields of the control frame are selected as specified in the 802.3x specification, and the pause time

(PT) value from this register is used in the pause time field of the control frame. The FCBBPA bit is

cleared by the hardware once the control frame is transferred onto the cable. The Host must make

sure that the busy bit is clear before writing to the register.

Ethernet MAC Flow Control (EMACFLOWCTL)

Base 0x400E.C000

Offset 0x018

Type RW, reset 0x0000.0000

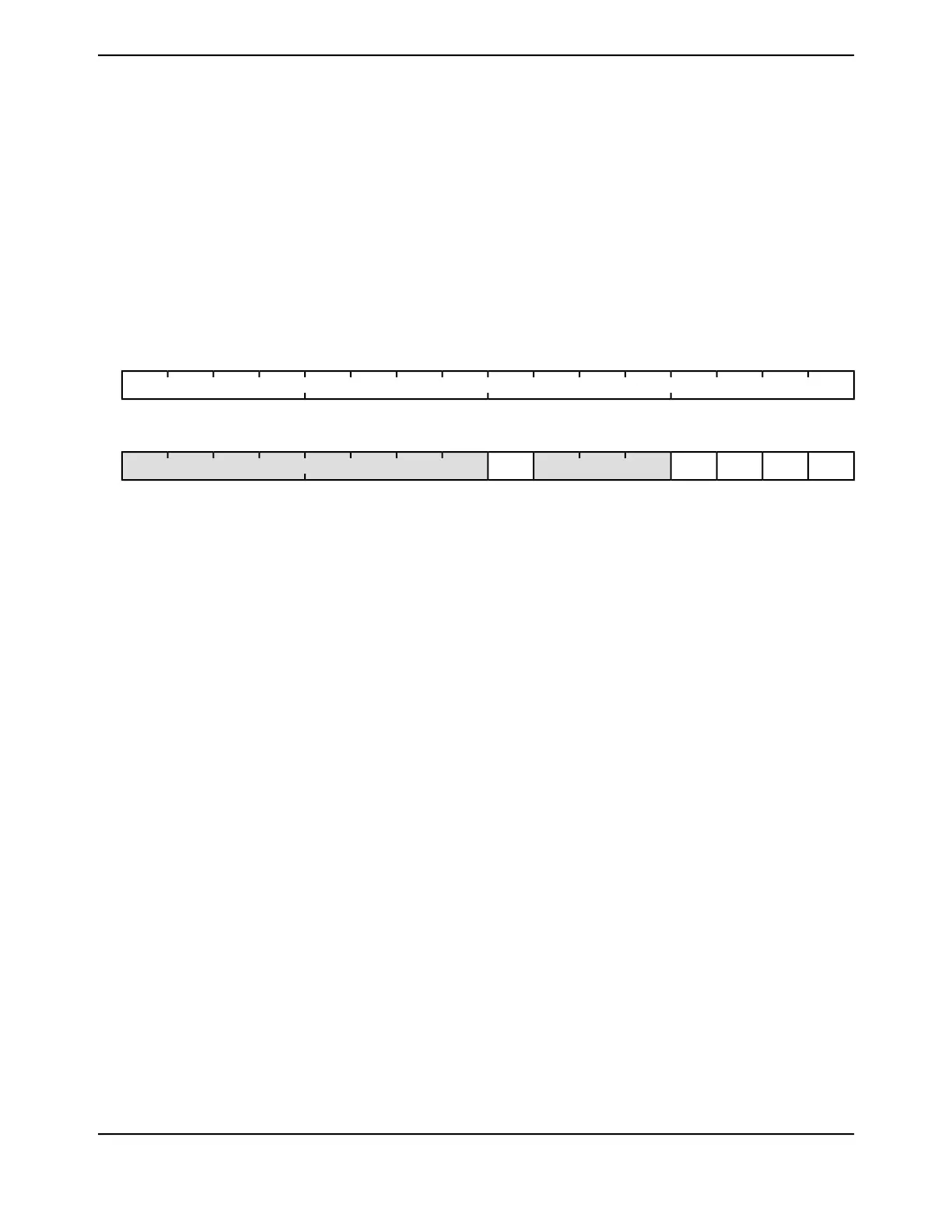

16171819202122232425262728293031

PT

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWRWType

0000000000000000Reset

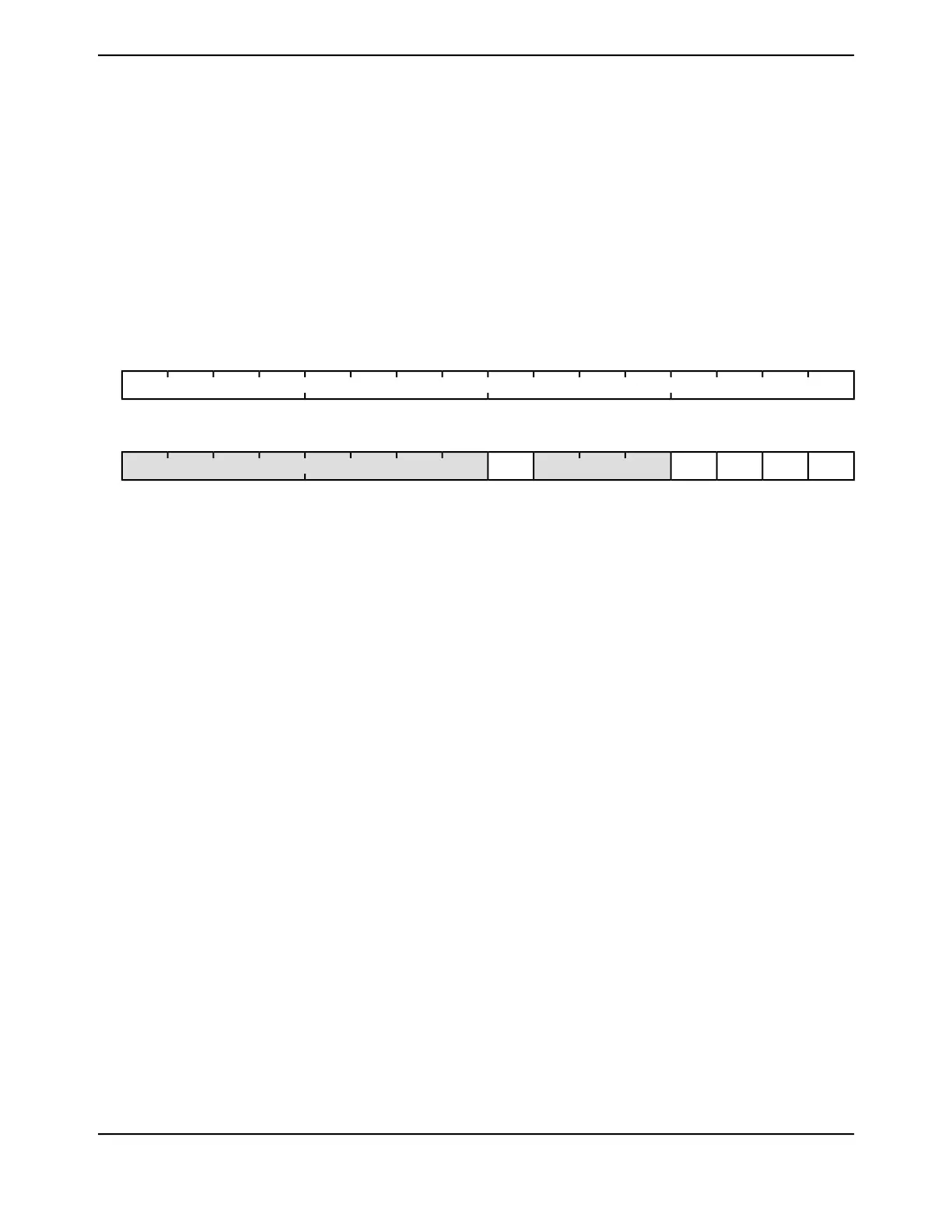

0123456789101112131415

FCBBPATFERFEUPreservedDZQPreserved

RWRWRWRWRORORORWROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Pause Time

This field holds the value to be used in the pause time field in the transmit

control frame.

For example, if these bits are set to 0x0100 then 256 slot times are used

in the Pause Time field in the transmit control frame.

0x0RWPT31:16

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved15:8

Disable Zero-Quanta Pause

When this bit is set, it disables the automatic generation of the

Zero-Quanta Pause Control frames on the deassertion of the flow-control

signal from the FIFO layer. When this bit is reset, normal operation with

automatic Zero-Quanta Pause Control frame generation is enabled.

DescriptionValue

Automatic Zero-Quanta Pause Control generation is enabled.0

Automatic Zero-Quanta Pause Control generation is disabled.1

0RWDZQP7

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved6:4

1487June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...