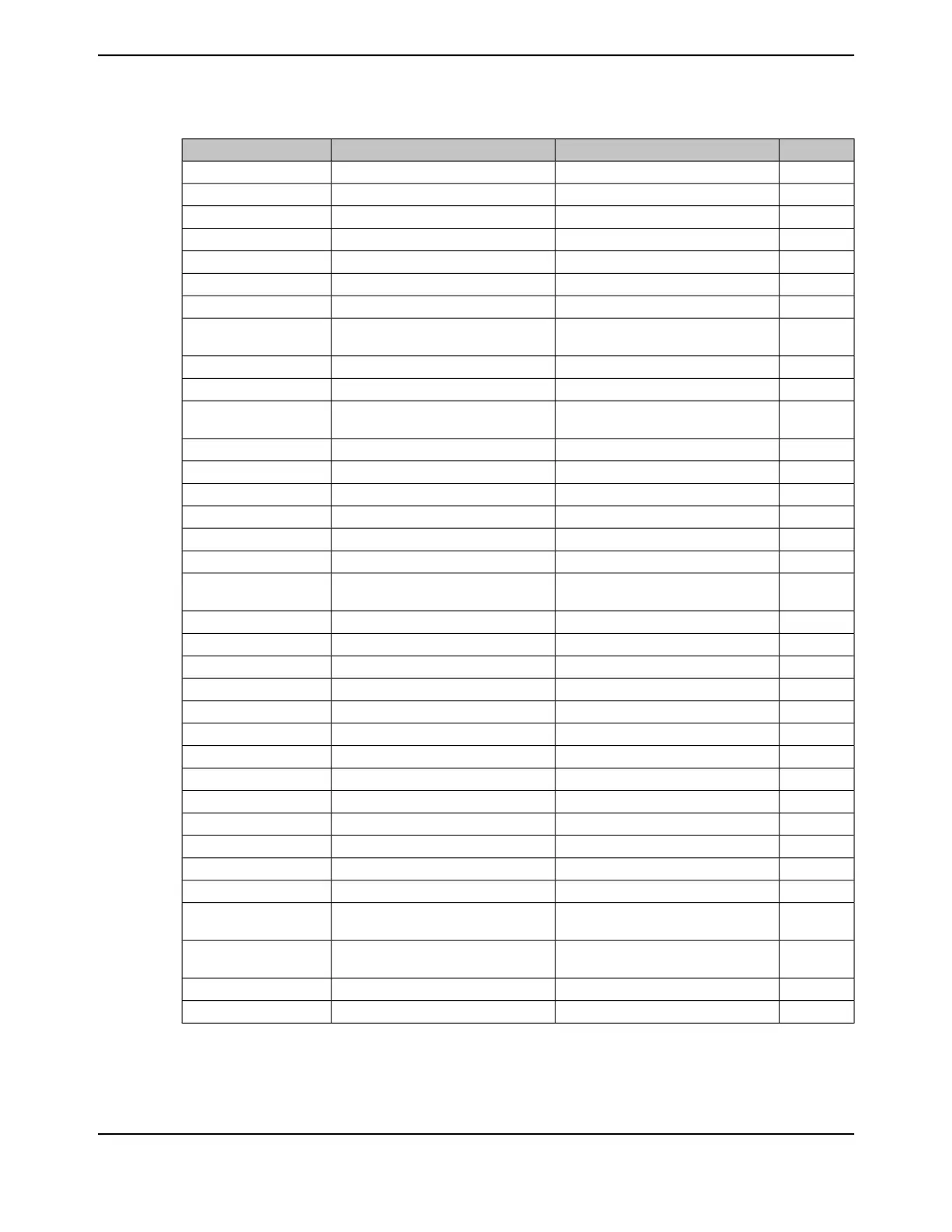

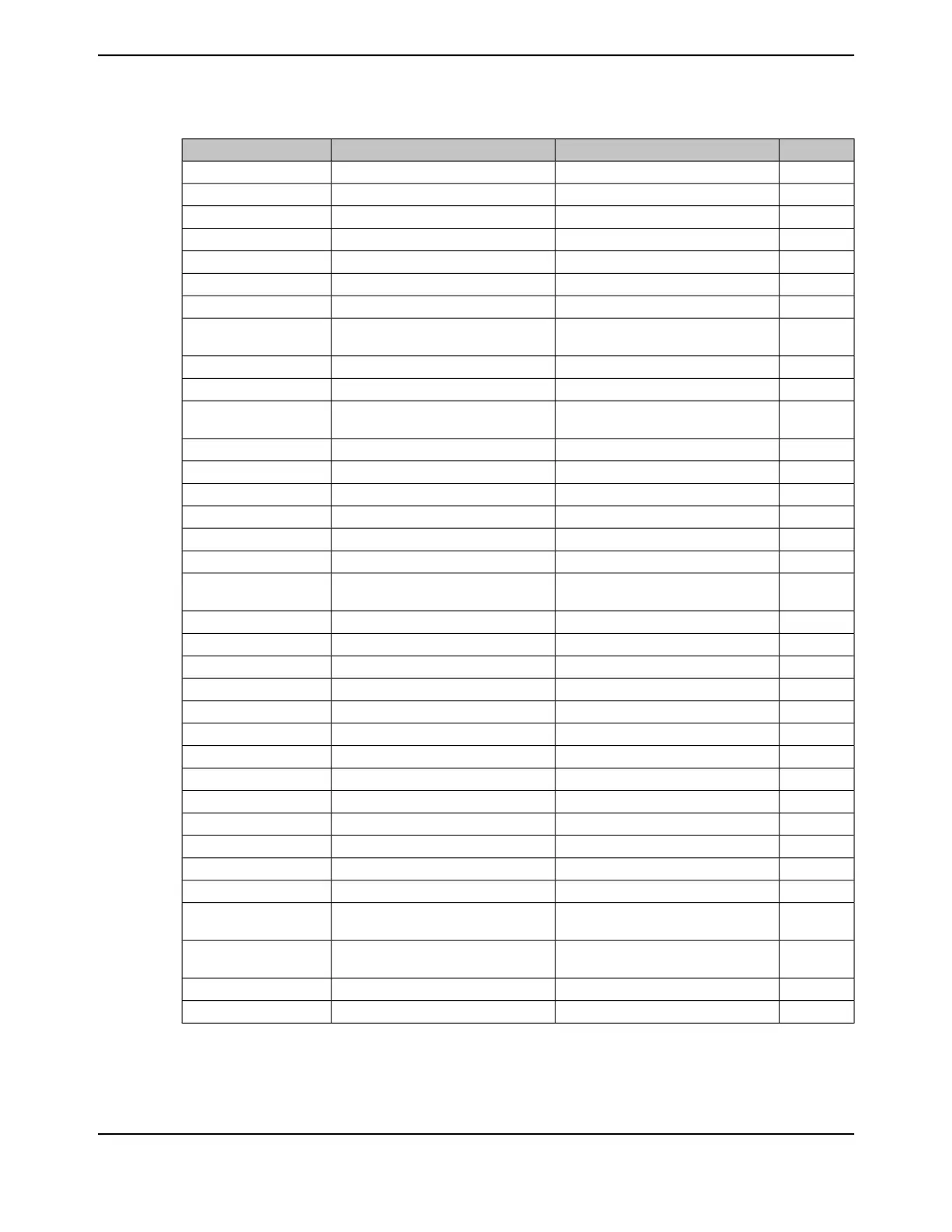

Table 2-13. Cortex-M4F Instruction Summary (continued)

FlagsBrief DescriptionOperandsMnemonic

N,Z,CLogical OR{Rd,} Rn, Op2ORR, ORRS

-Pack halfword{Rd,} Rn, Rm, Op2PKHTB, PKHBT

-Pop registers from stackreglistPOP

-Push registers onto stackreglistPUSH

QSaturating add{Rd,} Rn, RmQADD

-Saturating add 16{Rd,} Rn, RmQADD16

-Saturating add 8{Rd,} Rn, RmQADD8

-Saturating add and subtract with

exchange

{Rd,} Rn, RmQASX

QSaturating double and add{Rd,} Rn, RmQDADD

QSaturating double and subtract{Rd,} Rn, RmQDSUB

-Saturating subtract and add with

exchange

{Rd,} Rn, RmQSAX

QSaturating subtract{Rd,} Rn, RmQSUB

-Saturating subtract 16{Rd,} Rn, RmQSUB16

-Saturating subtract 8{Rd,} Rn, RmQSUB8

-Reverse bitsRd, RnRBIT

-Reverse byte order in a wordRd, RnREV

-Reverse byte order in each halfwordRd, RnREV16

-Reverse byte order in bottom halfword

and sign extend

Rd, RnREVSH

N,Z,CRotate rightRd, Rm, <Rs|#n>ROR, RORS

N,Z,CRotate right with extendRd, RmRRX, RRXS

N,Z,C,VReverse subtract{Rd,} Rn, Op2RSB, RSBS

GESigned add 16{Rd,} Rn, RmSADD16

GESigned add 8{Rd,} Rn, RmSADD8

GESigned add and subtract with exchange{Rd,} Rn, RmSASX

N,Z,C,VSubtract with carry{Rd,} Rn, Op2SBC, SBCS

-Signed bit field extractRd, Rn, #lsb, #widthSBFX

-Signed divide{Rd,} Rn, RmSDIV

-Select bytes{Rd,} Rn, RmSEL

-Send event-SEV

-Signed halving add 16{Rd,} Rn, RmSHADD16

-Signed halving add 8{Rd,} Rn, RmSHADD8

-Signed halving add and subtract with

exchange

{Rd,} Rn, RmSHASX

-Signed halving add and subtract with

exchange

{Rd,} Rn, RmSHSAX

-Signed halving subtract 16{Rd,} Rn, RmSHSUB16

-Signed halving subtract 8{Rd,} Rn, RmSHSUB8

129June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...