Register 11: UART Raw Interrupt Status (UARTRIS), offset 0x03C

The UARTRIS register is the raw interrupt status register. On a read, this register gives the current

raw status value of the corresponding interrupt. A write has no effect.

UART Raw Interrupt Status (UARTRIS)

UART0 base: 0x4000.C000

UART1 base: 0x4000.D000

UART2 base: 0x4000.E000

UART3 base: 0x4000.F000

UART4 base: 0x4001.0000

UART5 base: 0x4001.1000

UART6 base: 0x4001.2000

UART7 base: 0x4001.3000

Offset 0x03C

Type RO, reset 0x0000.0000

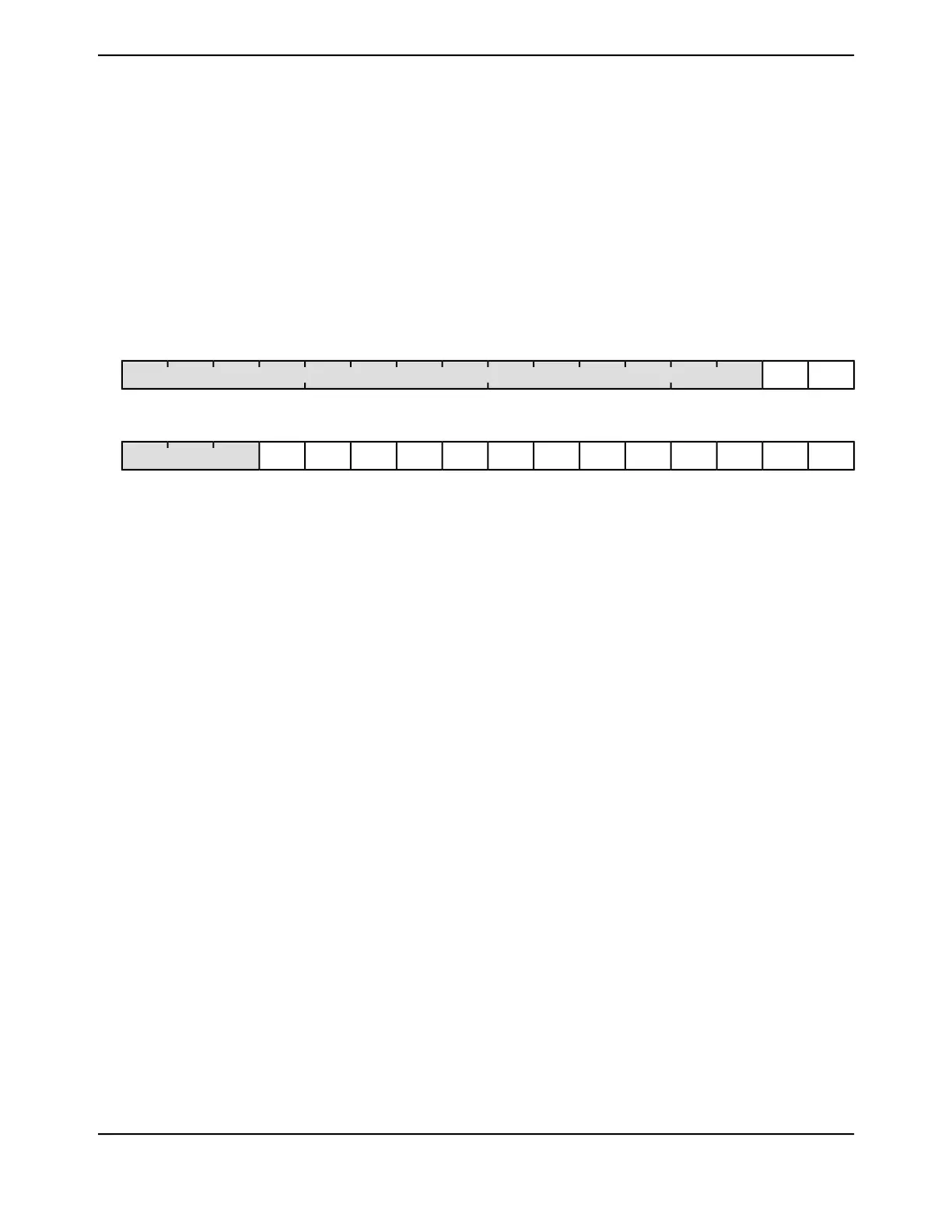

16171819202122232425262728293031

DMARXRISDMATXRIS

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

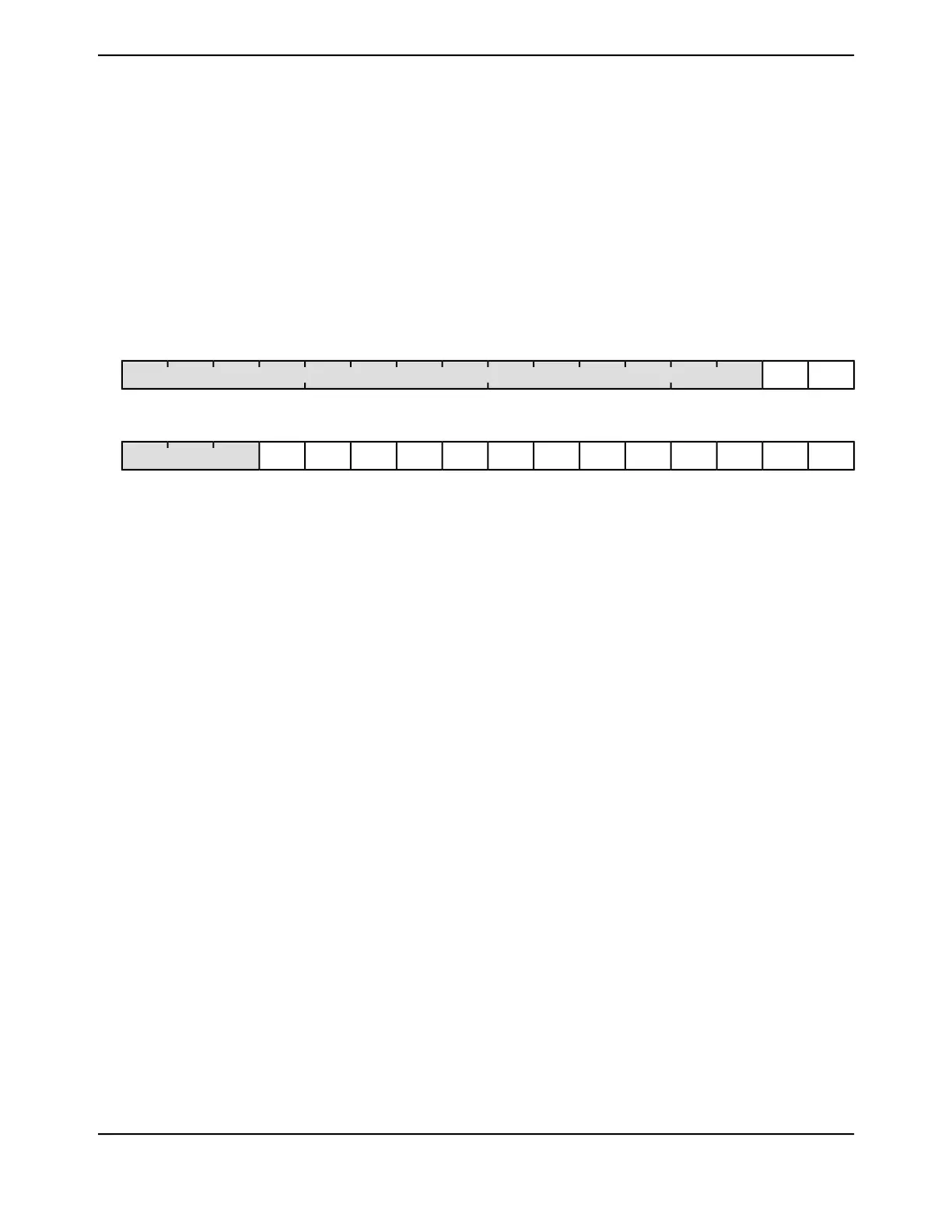

0123456789101112131415

RIRISCTSRISDCDRISDSRRISRXRISTXRISRTRISFERISPERISBERISOERISEOTRIS9BITRISreserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0ROreserved31:18

Transmit DMA Raw Interrupt Status

DescriptionValue

No interrupt0

The transmit DMA has completed.1

This bit is cleared by writing a 1 to the DMATXIC bit in the UARTICR

register.

0RODMATXRIS17

Receive DMA Raw Interrupt Status

DescriptionValue

No interrupt0

The receive DMA has completed.1

This bit is cleared by writing a 1 to the DMARXIC bit in the UARTICR

register.

0RODMARXRIS16

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0ROreserved15:13

June 18, 20141198

Texas Instruments-Production Data

Universal Asynchronous Receivers/Transmitters (UARTs)

Loading...

Loading...