Register 33: Ethernet MAC Receive Frame Count for CRC Error Frames

(EMACRXCNTCRCERR), offset 0x194

This register maintains the number of frames received with CRC error.

Note: This counter is reset to all zeros by setting the CNTRST bit in the Ethernet MAC MMC

Control (EMACMMCCTRL), offset 0x100.

Ethernet MAC Receive Frame Count for CRC Error Frames (EMACRXCNTCRCERR)

Base 0x400E.C000

Offset 0x194

Type RO, reset 0x0000.0000

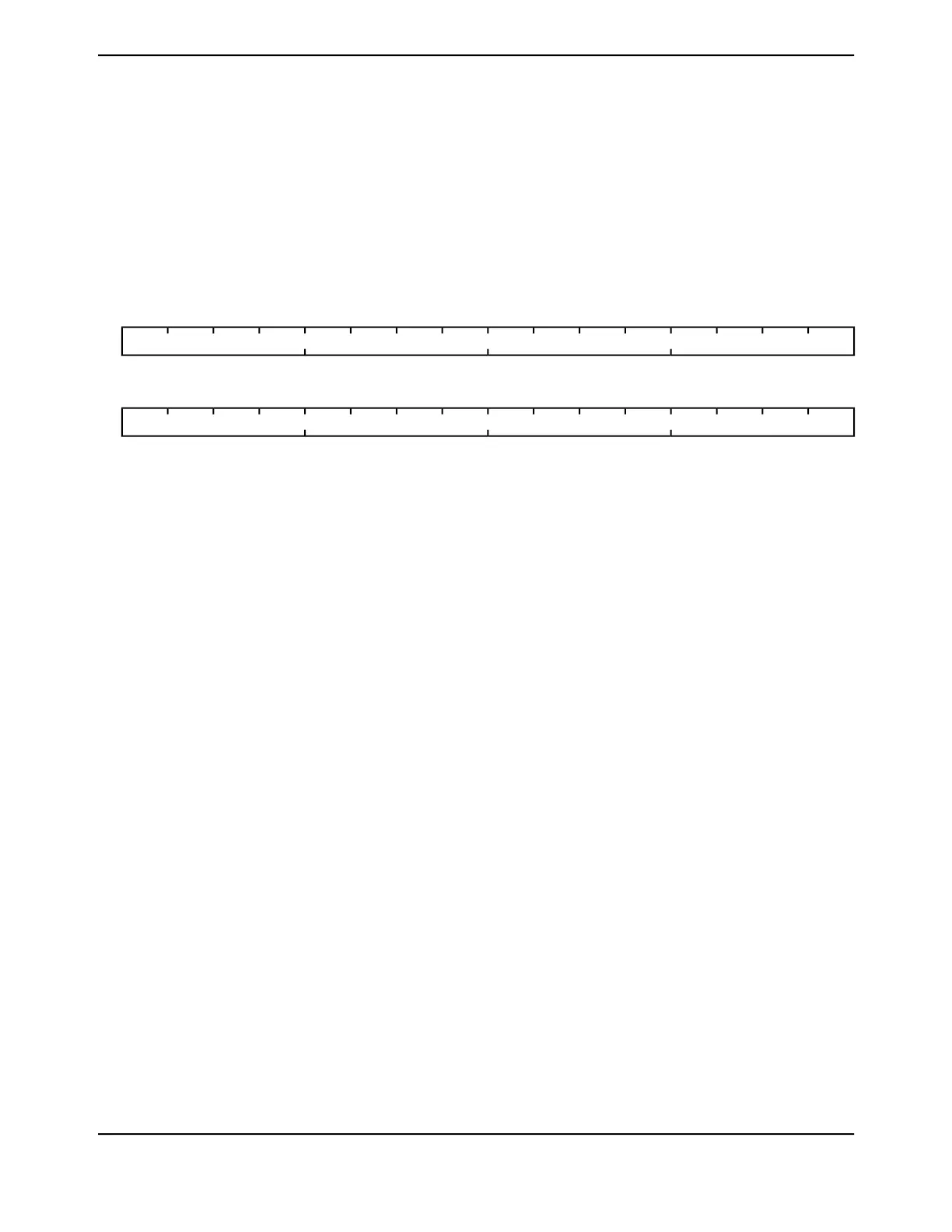

16171819202122232425262728293031

RXCRCERR

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

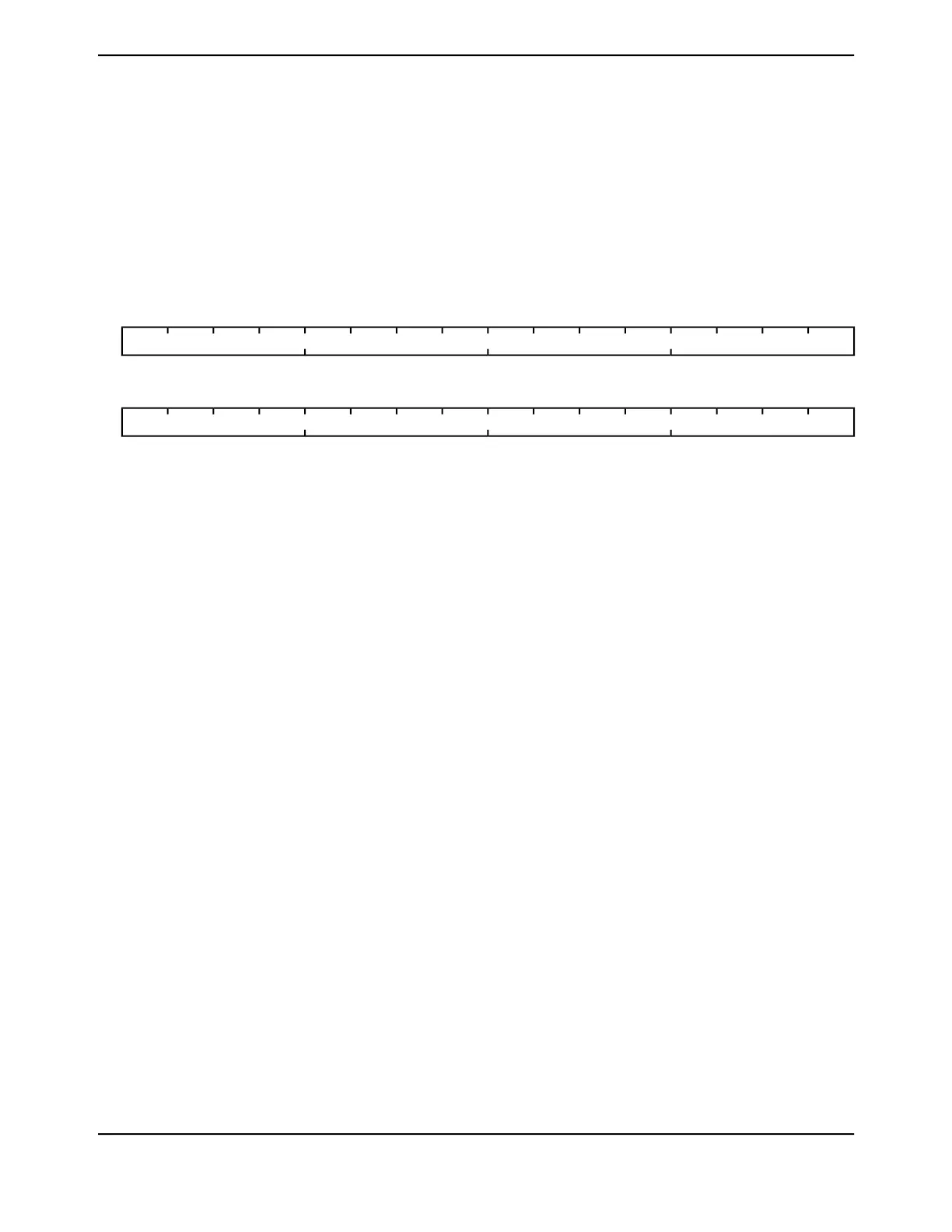

0123456789101112131415

RXCRCERR

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

This field indicates the number of frames received with CRC error.0x0RORXCRCERR31:0

June 18, 20141528

Texas Instruments-Production Data

Ethernet Controller

Loading...

Loading...