■ All 0s (INIT=0x2)

■ All 1s (INIT=0x3)

Once the operation is done, software should read the result from the CRC Post Processing Result

(CRCRSLTPP) register, offset 0x418, and a software channel μDMA interrupt should be used to

identify completion.

12.1.1.2 Data Size

The CRC module supports data being fed 32-bit words and 8 bits at a time and can dynamically

switch back and forth. The data size is configured by programming the SIZE bit in the CRCCTRL

register, offset 0x400.

Because CRC is a division on a long stream of bits, the application must take into consideration the

bit order. When processing message data that is read out by words, bit order is not an issue. For

example, if the data value in the message is 0x12345678, the most significant eight byte is 0x12

(00010010 in binary). If the data is processed as bytes, 0x12, 0x34, 0x56, and 0x78 are copied into

memory in that order and the word is stored as 0x78563412, where 0x12 is written as byte 0, 0x34

is written as byte 1, and so on.

12.1.1.3 Endian Configuration

The following endian configuration is provided by the ENDIAN field in the CRCCTRL register:

■ Swap byte in half-word

■ Swap half word

Input data width is four bytes, hence the configuration only affects the four-byte word. The ENDIAN

bit field supports the following configurations, assuming the input word is {B3, B2, B1, B0}

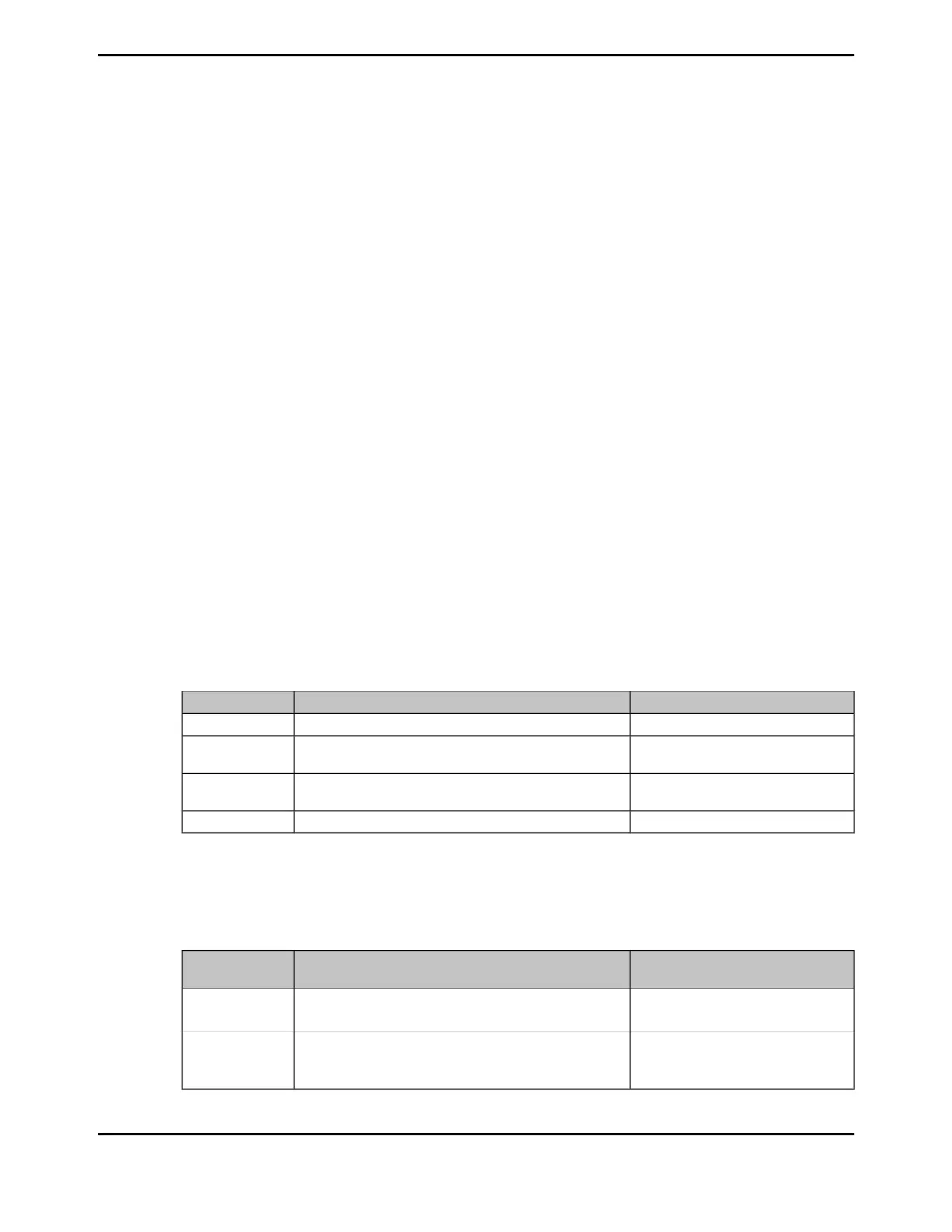

Table 12-1. Endian Configuration

ConfigurationDefinitionENDIAN Encoding

{B3, B2, B1, B0}Configuration unchanged.0x0

{B2, B3, B0, B1}Bytes are swapped in half-words but half-words are not

swapped

0x1

{B1, B0, B3, B2}Half-words are swapped but bytes are not swapped in

half-word.

0x2

{B0, B1, B2, B3}Bytes are swapped in half-words and half-words are swapped.0x3

Bit reversal is supported by the BR bit in the CRCCTRL register. The bit reversal operation works

in tandem with endian control. For example, the above table with the BR option set would look like

this:

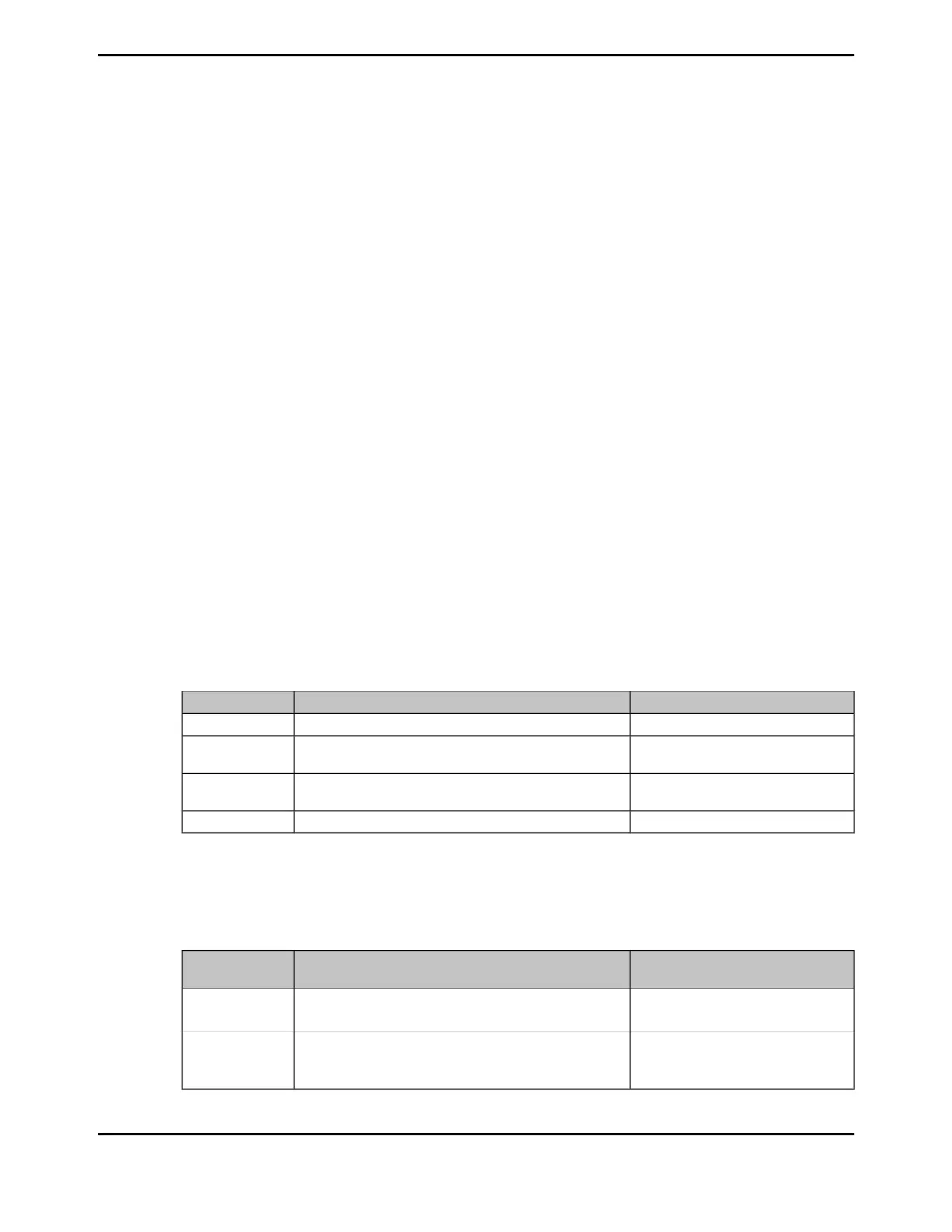

Table 12-2. Endian Configuration with Bit Reversal

Configuration with Bit Reversal (BR =

1)

Initial Endian ConfigurationENDIAN Encoding

B3[24:31],B2[16:23],B1[8:15],B0[0:7]Configuration unchanged.

{B3[31:24], B2[23:16] , B1[15:8], B0[7:0]}

0x0

B2[16:23],B3[24:31],B0[0:7],B1[8:15]Bytes are swapped in half-words but half-words are not

swapped

{B2[23:16], B3[31:24], B0[7:0], B1[15:8]}

0x1

947June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...