Register 28: ADC Sample Sequence 0 Sample and Hold Time (ADCSSTSH0),

offset 0x05C

This register controls the sample period size for each sample of sequencer 0. Each sample and

hold period select specifies the time allocated to the sample and hold circuit as shown by the

encodings in Table 15-3 on page 1058.

Note: If sampling the internal temperature sensor, the sample and hold width should be at least

16 ADC clocks (TSHn = 0x4).

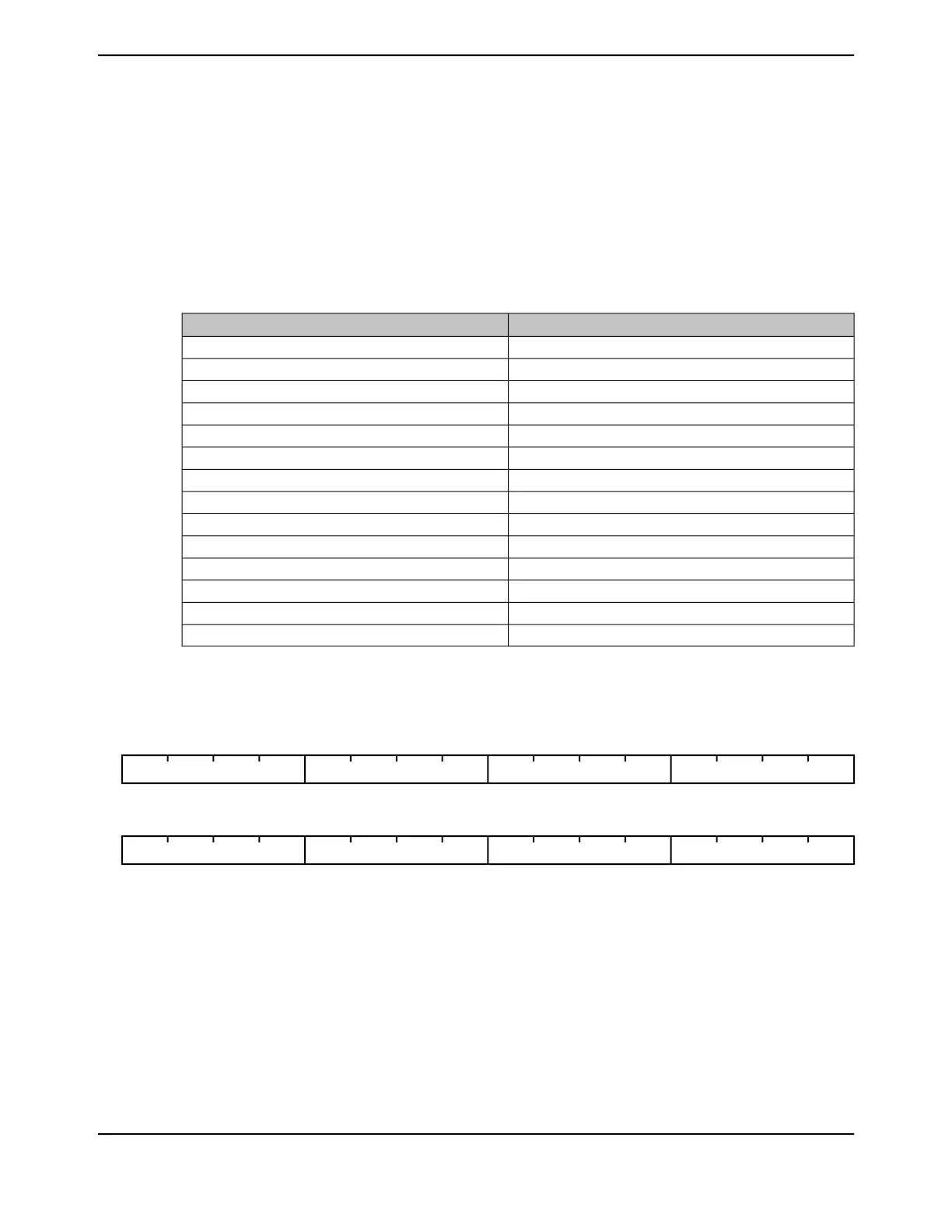

Table 15-8. Sample and Hold Width in ADC Clocks

N

SH

TSHn Encoding

40x0

reserved0x1

80x2

reserved0x3

160x4

reserved0x5

320x6

reserved0x7

640x8

reserved0x9

1280xA

reserved0xB

2560xC

reserved0xD-0xF

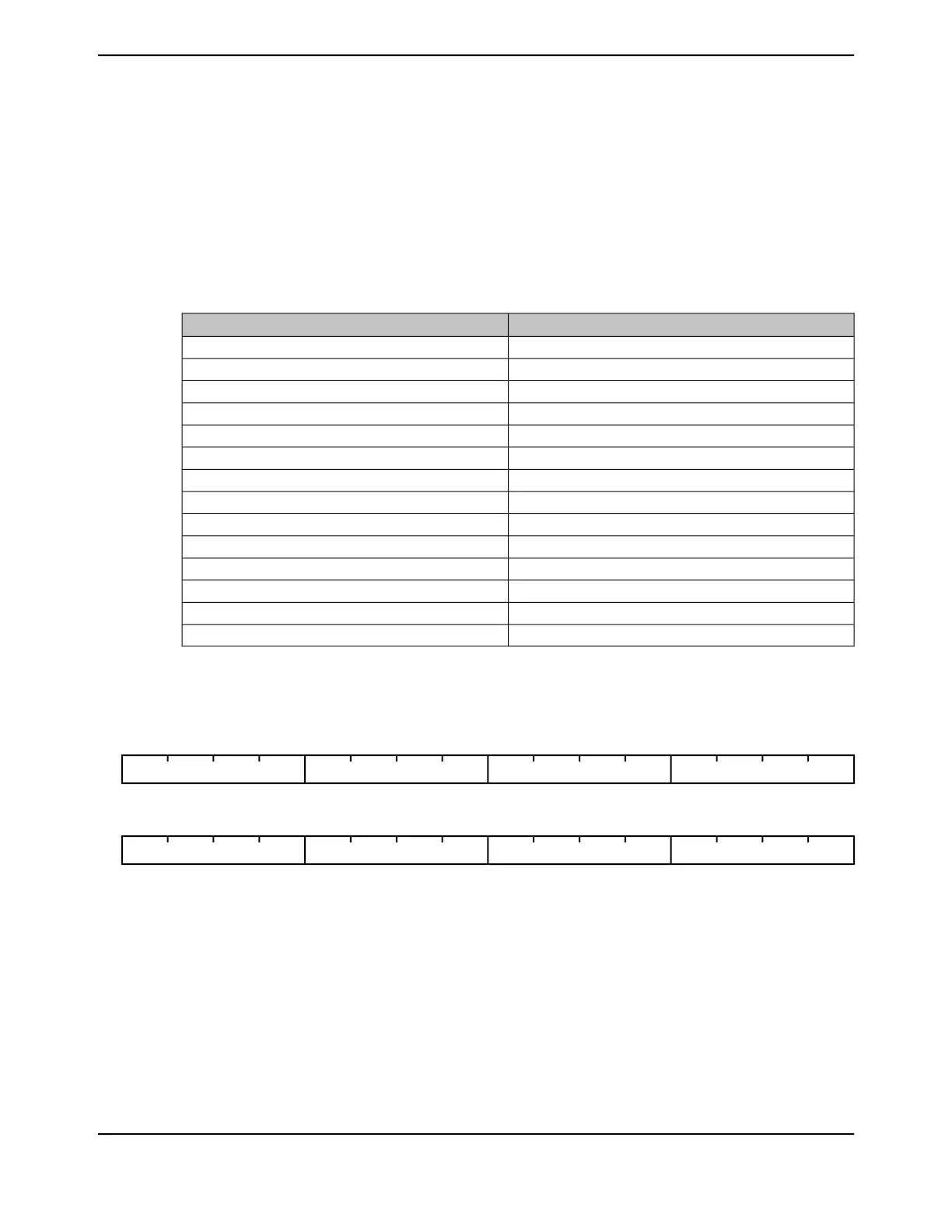

ADC Sample Sequence 0 Sample and Hold Time (ADCSSTSH0)

ADC0 base: 0x4003.8000

ADC1 base: 0x4003.9000

Offset 0x05C

Type RW, reset 0x0000.0000

16171819202122232425262728293031

TSH4TSH5TSH6TSH7

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWRWType

0000000000000000Reset

0123456789101112131415

TSH0TSH1TSH2TSH3

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWRWType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

8th Sample and Hold Period Select

The TSH7 field is used during the eighth sample of a sequence executed

with the sample sequencer.

0x0RWTSH731:28

7th Sample and Hold Period Select

The TSH6 field is used during the seventh sample of a sequence

executed with the sample sequencer.

0x0RWTSH627:24

1127June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...