Register 4: Watchdog Interrupt Clear (WDTICR), offset 0x00C

This register is the interrupt clear register. A write of any value to this register clears the Watchdog

interrupt and reloads the 32-bit counter from the WDTLOAD register. Write to this register when a

watchdog time-out interrupt has occurred to properly service the Watchdog. Value for a read or

reset is indeterminate.

Note: Locking the watchdog registers by using the WDTLOCK register does not affect the WDTICR

register and allows interrupts to always be serviced. Thus, a write at any time of the WDTICR

register clears the WDTMIS register and reloads the 32-bit counter from the WDTLOAD

register. The WDTICR register should only be written when interrupts have triggered and

need to be serviced.

Watchdog Interrupt Clear (WDTICR)

WDT0 base: 0x4000.0000

WDT1 base: 0x4000.1000

Offset 0x00C

Type WO, reset -

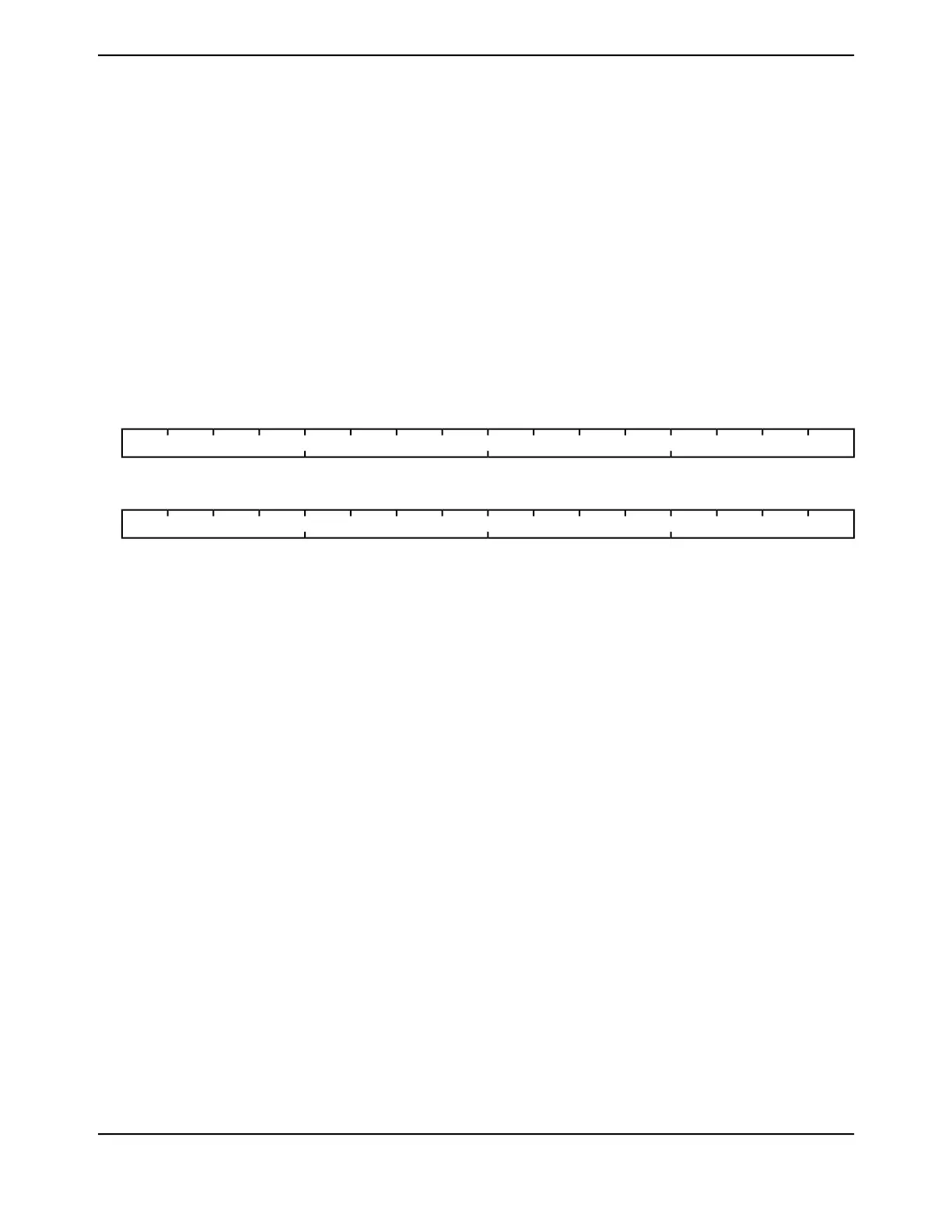

16171819202122232425262728293031

WDTINTCLR

WOWOWOWOWOWOWOWOWOWOWOWOWOWOWOWOType

----------------Reset

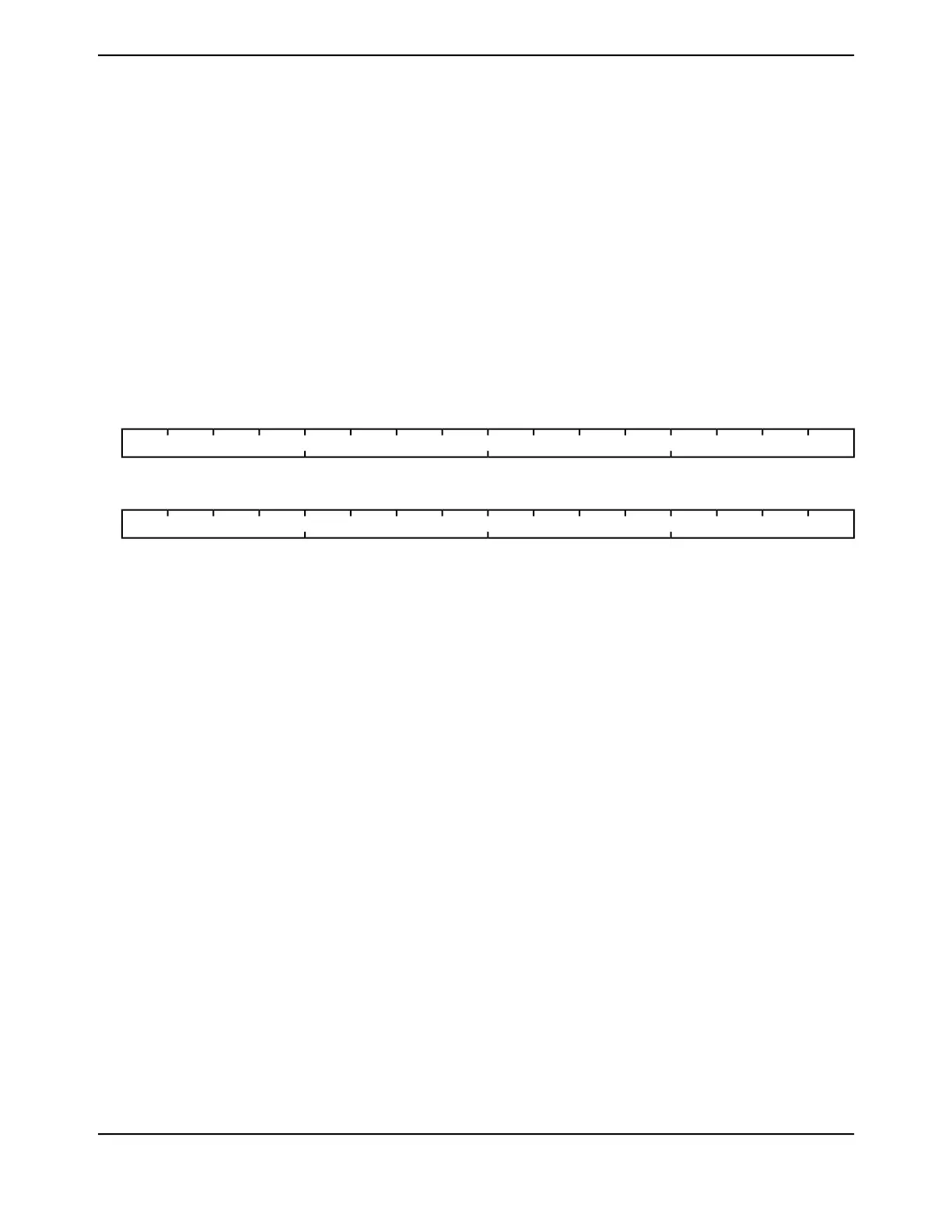

0123456789101112131415

WDTINTCLR

WOWOWOWOWOWOWOWOWOWOWOWOWOWOWOWOType

----------------Reset

DescriptionResetTypeNameBit/Field

Watchdog Interrupt Clear

A write of any value to this register clears the Watchdog interrupt and

reloads the 32-bit counter from the WDTLOAD register. Write to this

register when a watchdog time-out interrupt has occurred to properly

service the Watchdog. Value for a read or reset is indeterminate.

-WOWDTINTCLR31:0

June 18, 20141036

Texas Instruments-Production Data

Watchdog Timers

Loading...

Loading...