FIFO mode accesses are the same as normal read and write accesses, except that the ALE signal

and address pins are not present. Two input signals can be used to indicate when the XFIFO is full

or empty to gate transactions and avoid overruns and underruns. The FFULL and FEMPTY signals

are synchronized and must be recognized as asserted by the microcontroller for 2 system clocks

before they affect transaction status. The MAXWAIT field in the EPIHBnCFG register defines the

maximum number of EPI clocks to wait while the FEMPTY or FFULL signal is holding off a transaction.

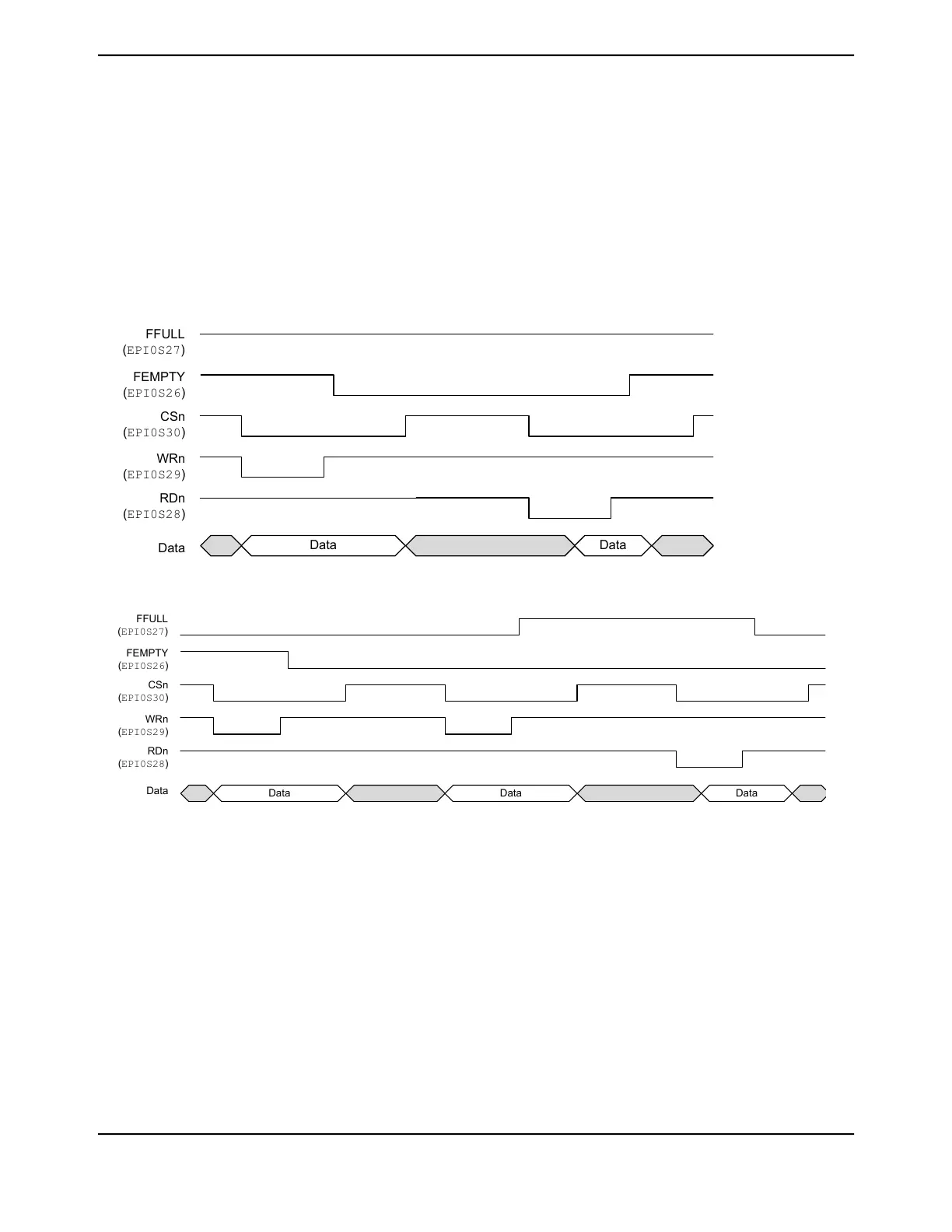

Figure 11-17 on page 847 shows how the FEMPTY signal should respond to a write and read from

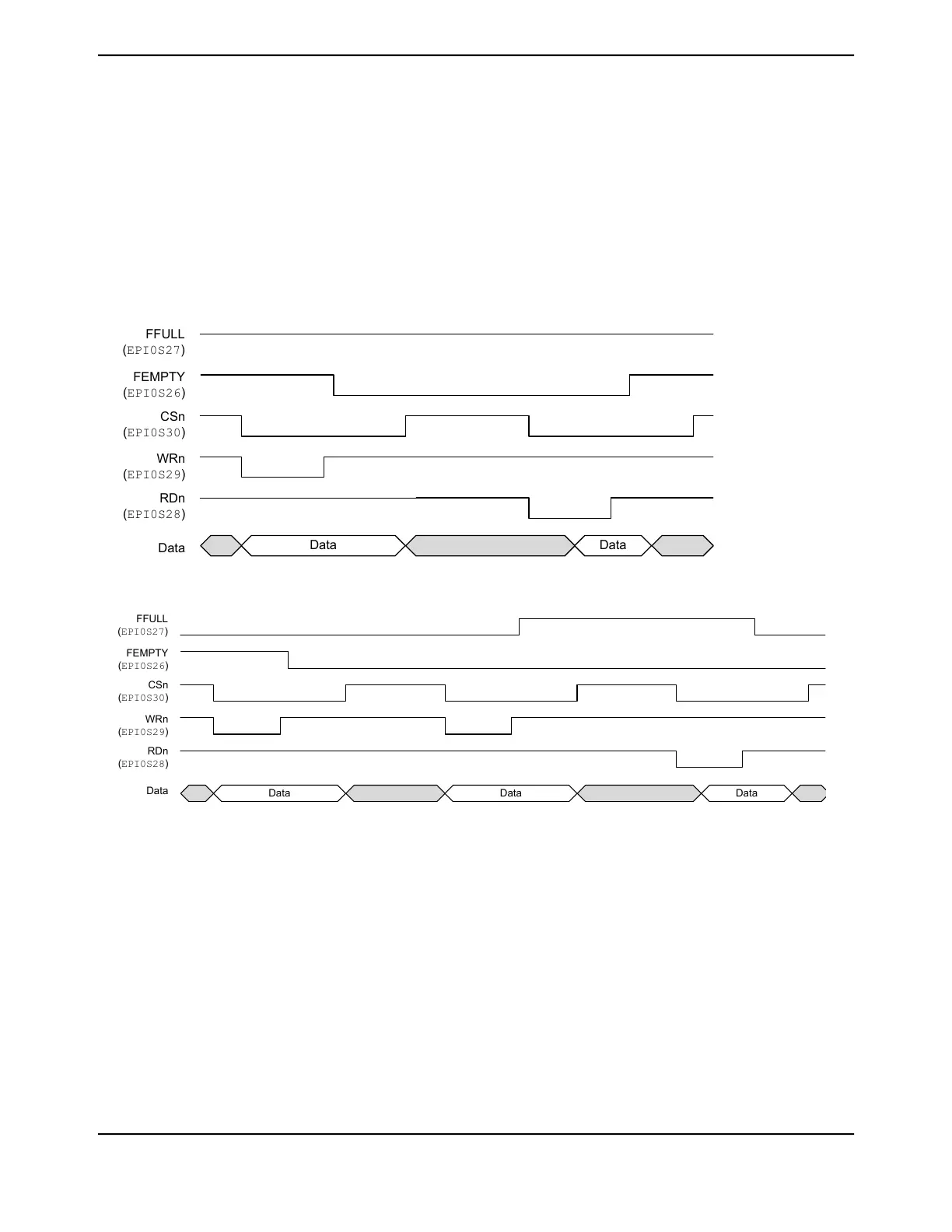

the XFIFO. Figure 11-18 on page 847 shows how the FEMPTY and FFULL signals should respond

to 2 writes and 1 read from an external FIFO that contains two entries.

Figure 11-17. Write Followed by Read to External FIFO

FFULL

(EPI0S27)

FEMPTY

(EPI0S26)

CSn

(EPI0S30)

WRn

(EPI0S29)

RDn

(EPI0S28)

Data

Data Data

Figure 11-18. Two-Entry FIFO

FFULL

(EPI0S27)

FEMPTY

(EPI0S26)

CSn

(EPI0S30)

WRn

(EPI0S29)

RDn

(EPI0S28)

Data

Data Data Data

11.4.4 General-Purpose Mode

The General-Purpose Mode Configuration (EPIGPCFG) register is used to configure the control,

data, and address pins, if used. Any unused EPI controller signals can be used as GPIOs or another

alternate function. The general-purpose configuration can be used for custom interfaces with FPGAs,

CPLDs, and digital data acquisition and actuator control.

General-Purpose mode is designed for three general types of use:

■ Extremely high-speed clocked interfaces to FPGAs and CPLDs. Three sizes of data and optional

address are supported. Framing and clock-enable functions permit more optimized interfaces.

■ General parallel GPIO. From 1 to 32 pins may be written or read, with the speed precisely

controlled by the EPIBAUD register baud rate (when used with the WFIFO and/or the NBRFIFO)

or by the rate of accesses from software or μDMA. Examples of this type of use include:

847June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...