Register 19: PLL Frequency 0 (PLLFREQ0), offset 0x160

This register always contains the variables used to configure the PLL. If the PLL is reprogrammed,

it must go through a relock sequence which is defined by the parameter T

READY

in Table

27-16 on page 1835. When controlling this register directly, software must change this value while the

PLL is powered down. Writes to PLLFREQ0 are delayed from affecting the PLL until the RSCLKCFG

register NEWFREQ bit is written with a 1.

The PLL frequency can be calculated using the following equation:

f

VCO

= (f

IN

* MDIV)

where

f

IN

= f

XTAL

/(Q+1)(N+1) or f

PIOSC

/(Q+1)(N+1)

MDIV = MINT + (MFRAC / 1024)

The Q and N values are programmed in the PLLFREQ1 register. Note that to reduce jitter, MFRAC

should be programmed to 0x0.

PLL Frequency 0 (PLLFREQ0)

Base 0x400F.E000

Offset 0x160

Type RW, reset 0x0000.0000

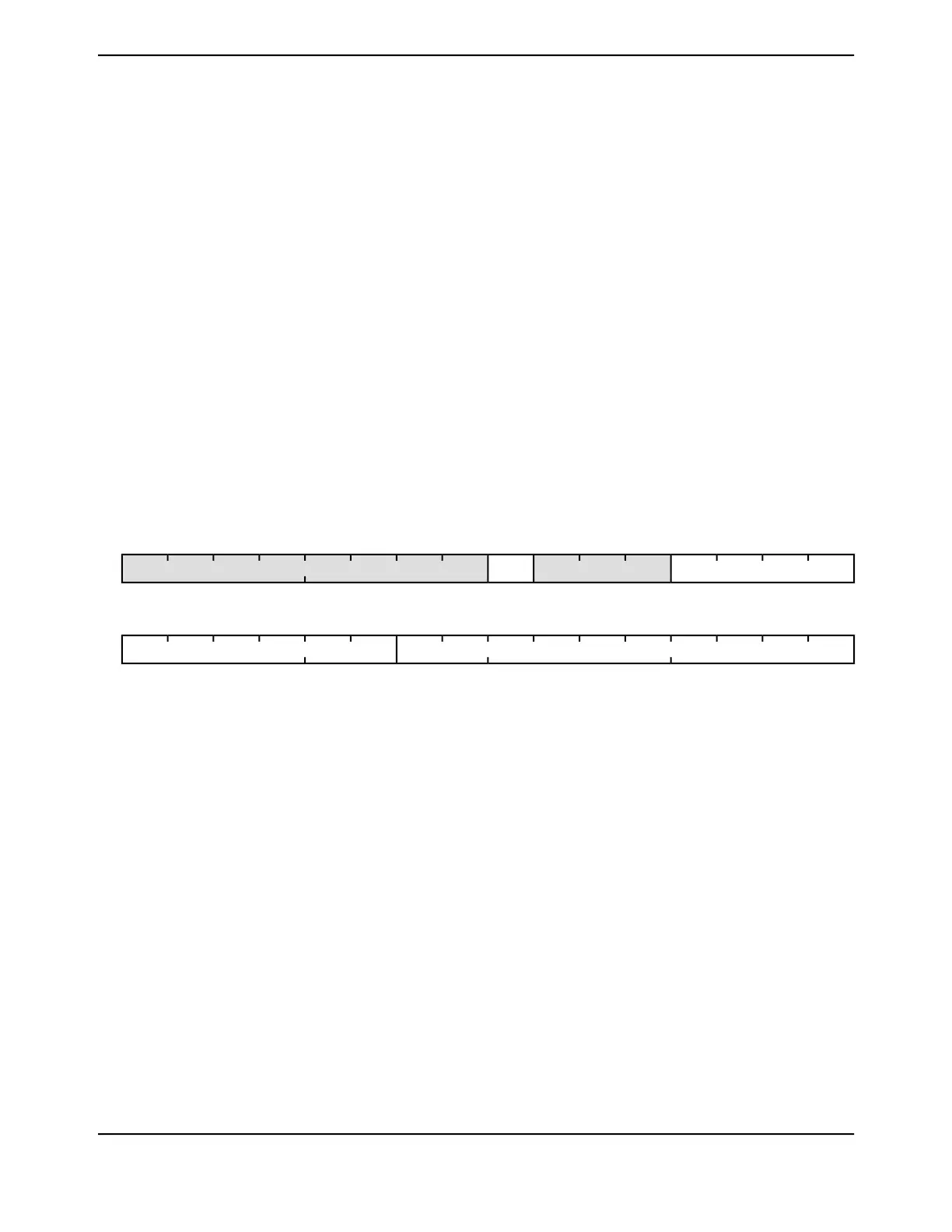

16171819202122232425262728293031

MFRACreservedPLLPWRreserved

RWRWRWRWRORORORWROROROROROROROROType

0000000000000000Reset

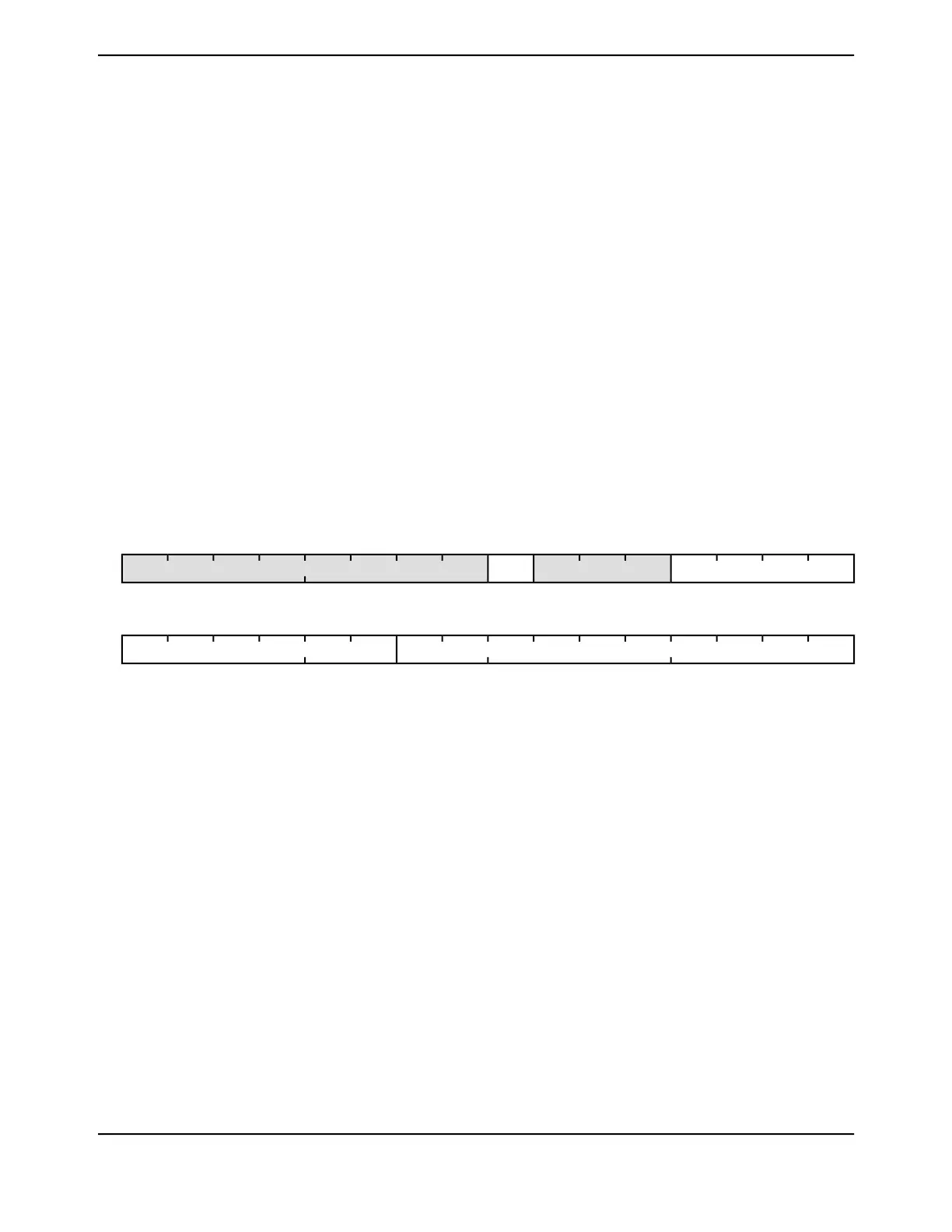

0123456789101112131415

MINTMFRAC

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWRWType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x000ROreserved31:24

PLL Power

This bit controls power to the PLL. If set, the PLL power is applied and

the PLL will oscillate based on the values in the PLLFREQ0 and

PLLFREQ1 registers.

0RWPLLPWR23

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved22:20

PLL M Fractional Value0RWMFRAC19:10

PLL M Integer Value

This field contains the integer value of the PLL M value.

0x00RWMINT9:0

June 18, 2014292

Texas Instruments-Production Data

System Control

Loading...

Loading...