Register 1: GPTM Configuration (GPTMCFG), offset 0x000

This register configures the global operation of the GPTM module. The value written to this register

determines whether the GPTM is in 32- or 16-bit mode.

Important: Bits in this register should only be changed when the TAEN and TBEN bits in the

GPTMCTL register are cleared.

GPTM Configuration (GPTMCFG)

16/32-bit Timer 0 base: 0x4003.0000

16/32-bit Timer 1 base: 0x4003.1000

16/32-bit Timer 2 base: 0x4003.2000

16/32-bit Timer 3 base: 0x4003.3000

16/32-bit Timer 4 base: 0x4003.4000

16/32-bit Timer 5 base: 0x4003.5000

16/32-bit Timer 6 base: 0x400E.0000

16/32-bit Timer 7 base: 0x400E.1000

Offset 0x000

Type RW, reset 0x0000.0000

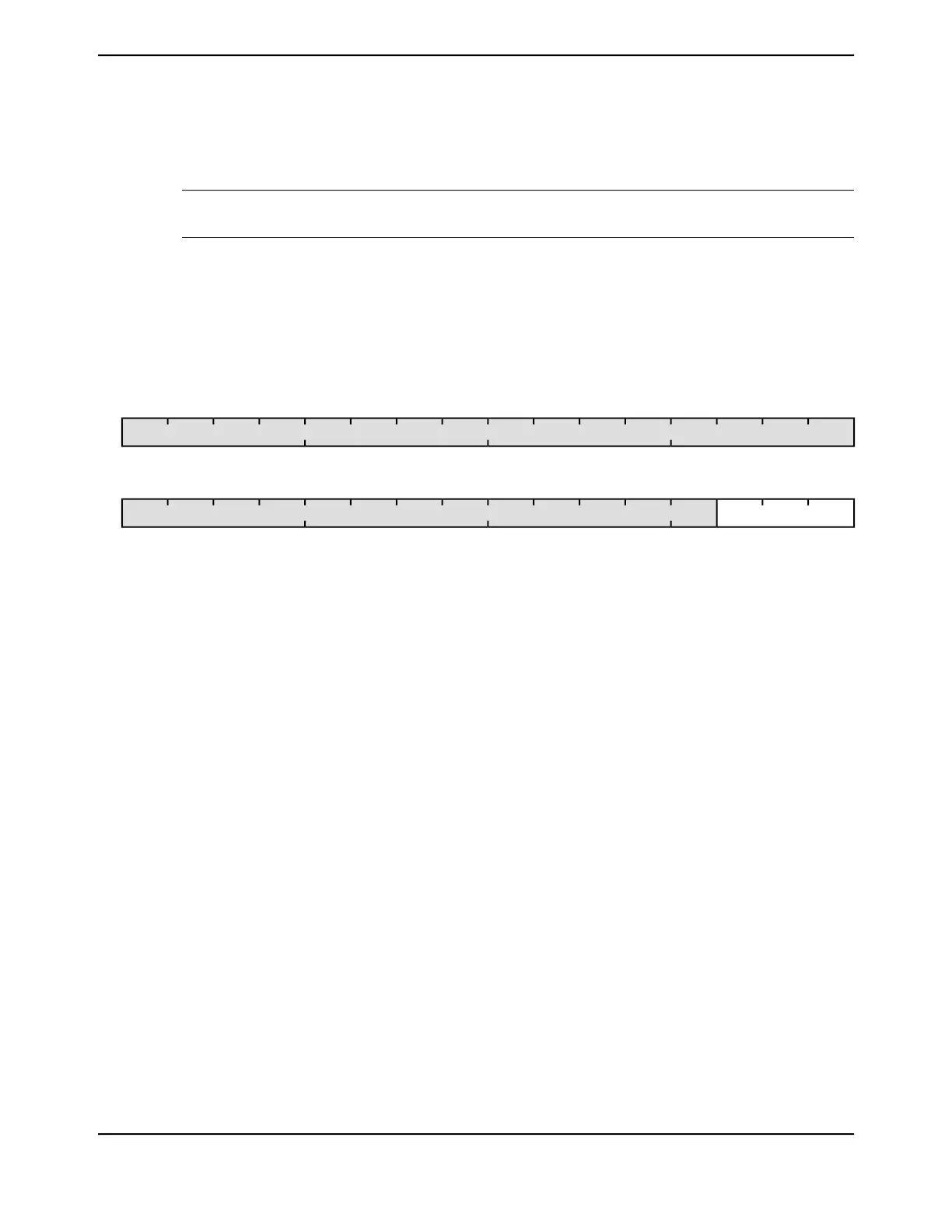

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

0123456789101112131415

GPTMCFGreserved

RWRWRWROROROROROROROROROROROROROType

0000000000000000Reset

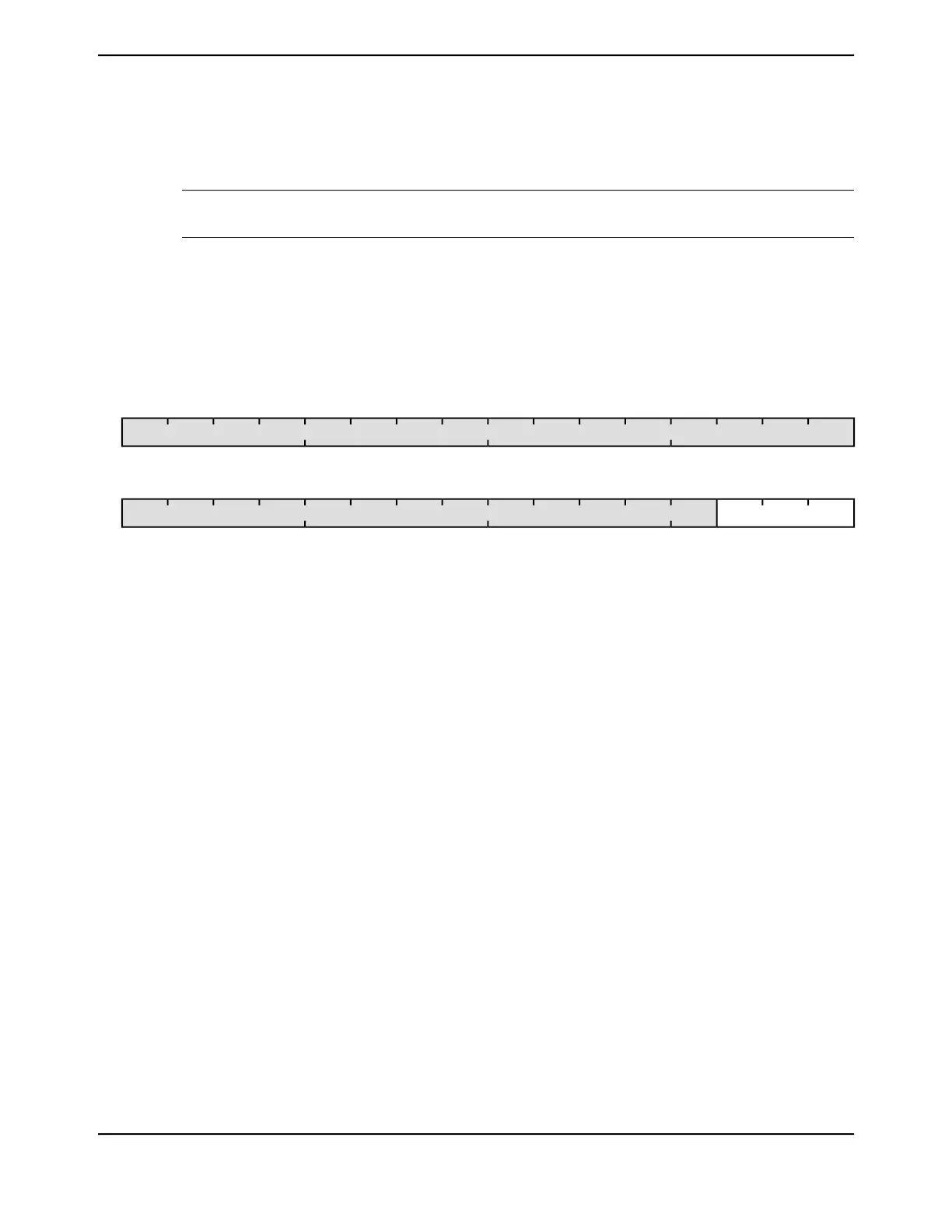

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.000ROreserved31:3

GPTM Configuration

The GPTMCFG values are defined as follows:

DescriptionValue

For a 16/32-bit timer, this value selects the 32-bit timer

configuration.

0x0

For a 16/32-bit timer, this value selects the 32-bit real-time

clock (RTC) counter configuration.

0x1

Reserved0x2-0x3

For a 16/32-bit timer, this value selects the 16-bit timer

configuration.

The function is controlled by bits 1:0 of GPTMTAMR and

GPTMTBMR.

0x4

Reserved0x5-0x7

0x0RWGPTMCFG2:0

June 18, 2014976

Texas Instruments-Production Data

General-Purpose Timers

Loading...

Loading...