Register 67: Memory Management Fault Address (MMADDR), offset 0xD34

Note: This register can only be accessed from privileged mode.

The MMADDR register contains the address of the location that generated a memory management

fault. When an unaligned access faults, the address in the MMADDR register is the actual address

that faulted. Because a single read or write instruction can be split into multiple aligned accesses,

the fault address can be any address in the range of the requested access size. Bits in the Memory

Management Fault Status (MFAULTSTAT) register indicate the cause of the fault and whether

the value in the MMADDR register is valid (see page 184).

Memory Management Fault Address (MMADDR)

Base 0xE000.E000

Offset 0xD34

Type RW, reset -

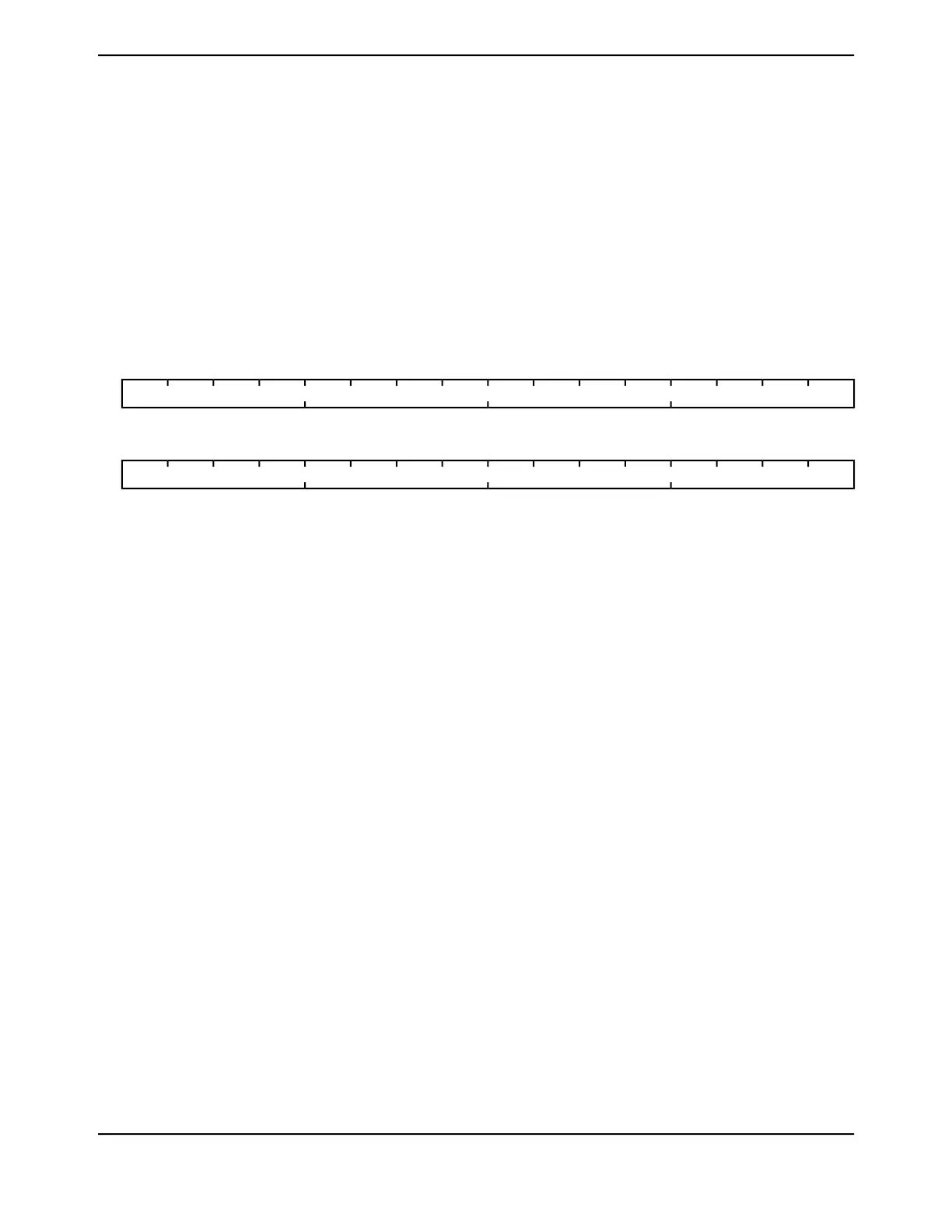

16171819202122232425262728293031

ADDR

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWRWType

----------------Reset

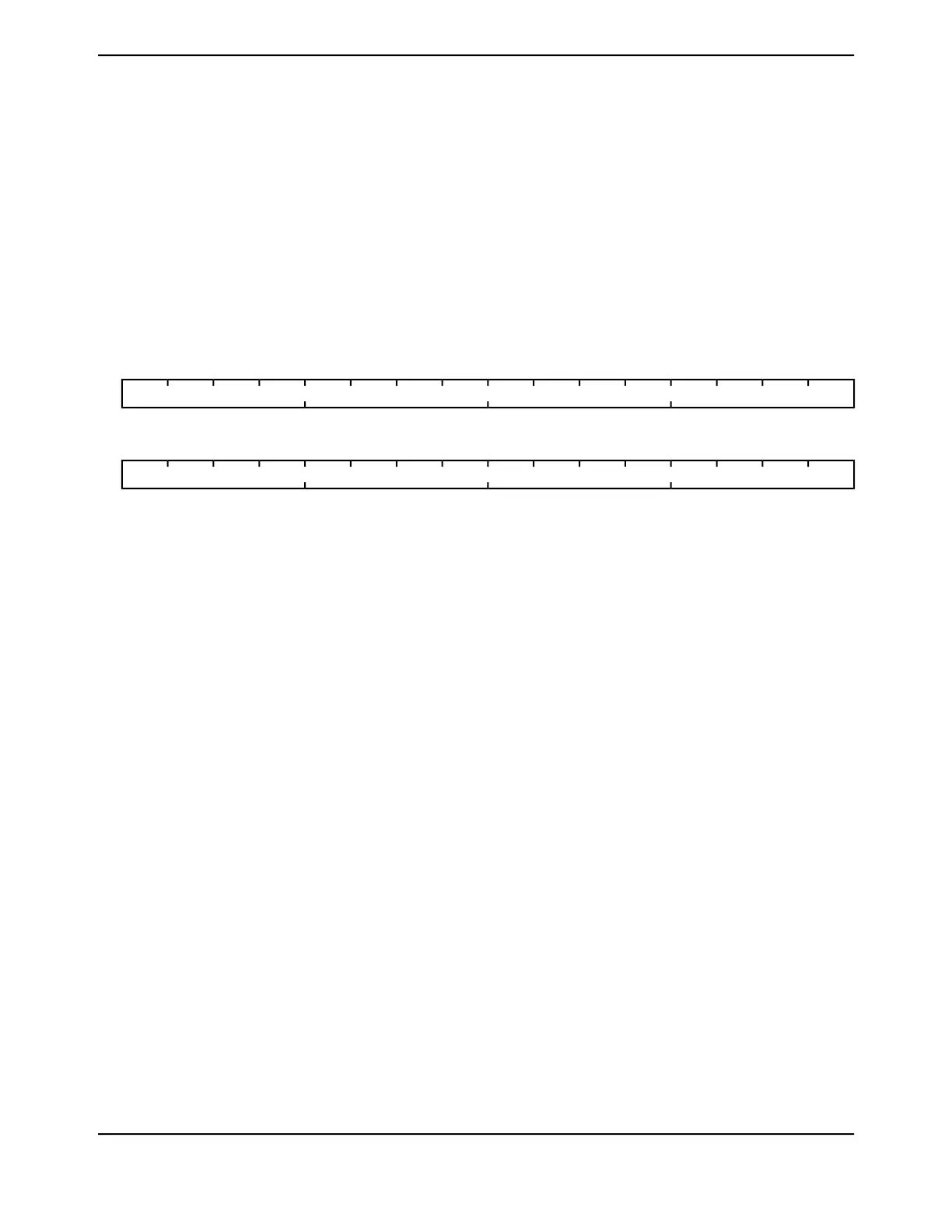

0123456789101112131415

ADDR

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWRWType

----------------Reset

DescriptionResetTypeNameBit/Field

Fault Address

When the MMARV bit of MFAULTSTAT is set, this field holds the address

of the location that generated the memory management fault.

-RWADDR31:0

191June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...