7. Set the WRCRE bit in the EPIHB16CFGn register to initiate a write from the EPIHBPSRAM

register to PSRAM's CR register.

Note: If the PSRAM's CR register must be reprogrammed after initialization, the application should

allow the previous transfer to complete before beginning configuration to ensure proper

PSRAM functionality.

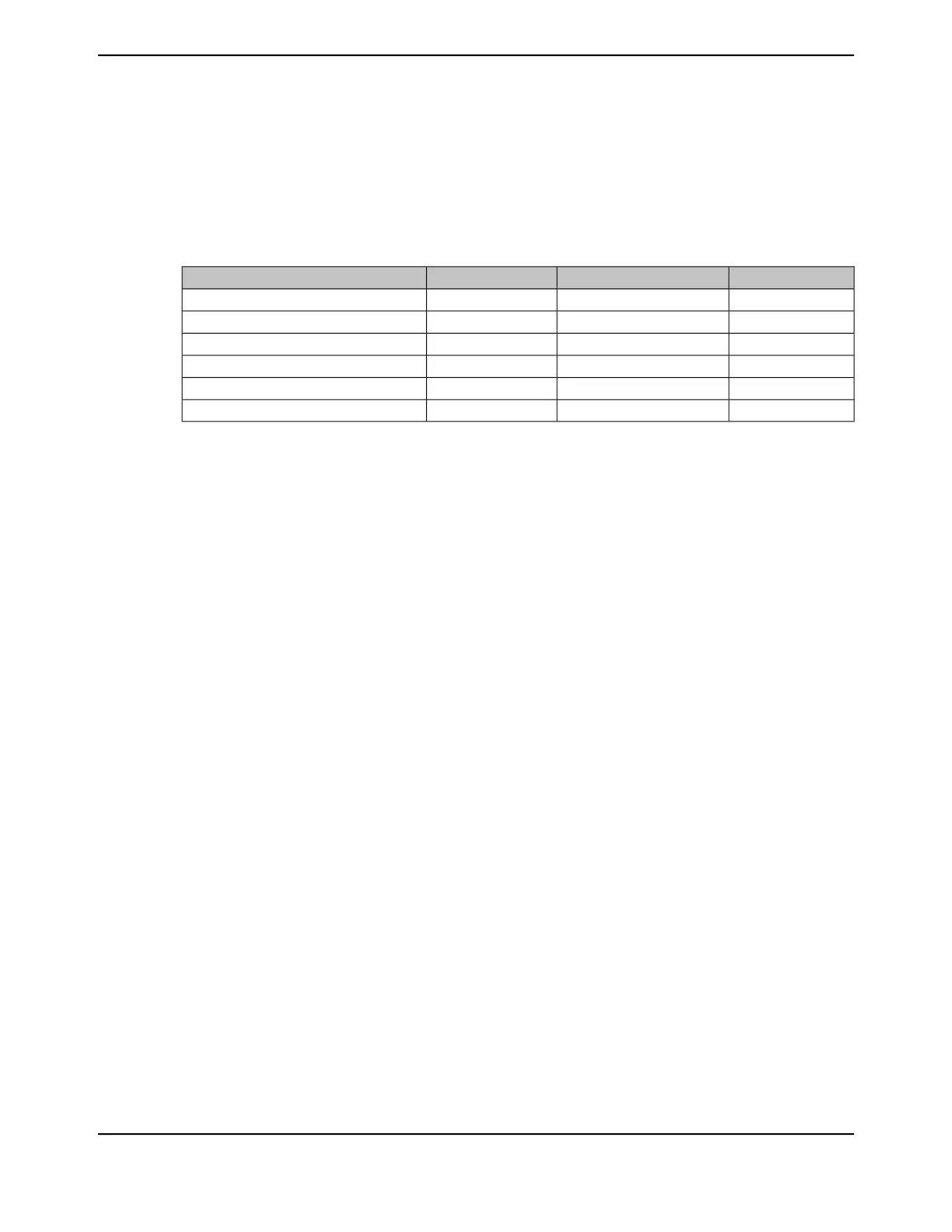

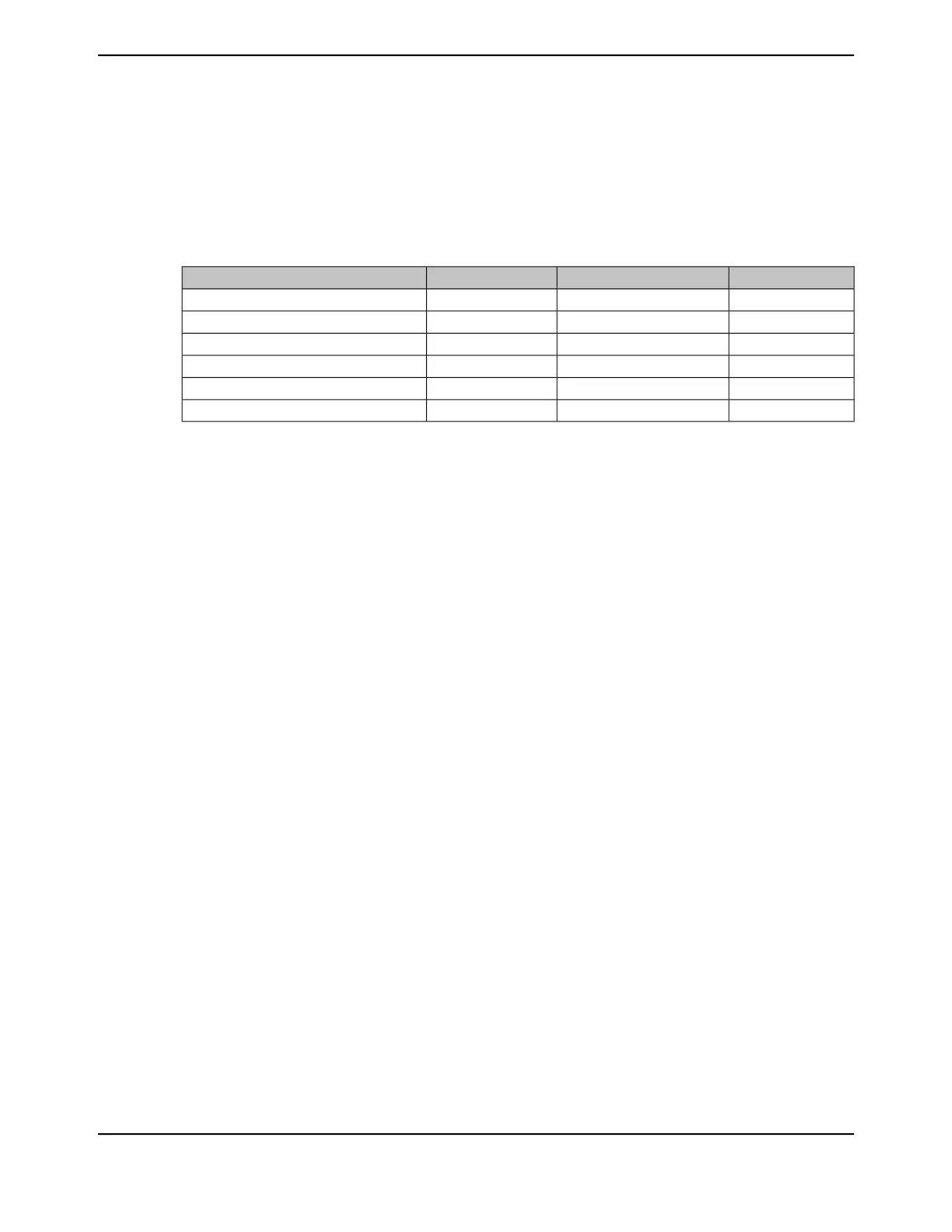

Table 11-10. PSRAM Fixed Latency Wait State Configuration

RWSM/WRWSMRDWS[1:0]/WRWS[1:0]Latency in ClocksLatency Counter

00x03BCR Code 2

10x14BCR Code 3

00x15BCR Code 4

10x26BCR Code 5

00x27BCR Code 6

00x39BCR Code 8

In variable initial latency mode, the memory's WAIT (iRDY) pin guides the EPI module when to read

and write. The WAIT (iRDY) pin stalls the access for the duration of the latency and adds cycles if

there is a refresh collision. To get the best performance, set CR[13:11] = 0x2, the WRWS field of

the EPIHB16CFG register to 0x0, and the WRWSM and RDWSM bit of the EPI16TIMEn register to 0.

For the WAIT pin to be recognized correctly set the IRDYDLY bit in the EPI16TIMEn register to 1

and the CR[8] =1 in the EPIHBPSRAM register.

Note: Wait state latency works differently in PSRAM Burst mode than in other modes. In PSRAM

Burst mode the RDWS and WRWS bit fields define the latency for only the first access of the

write or read cycle. Every access after that is a single access.

Figure 11-7 on page 839 and Figure 11-8 on page 839 depict a PSRAM burst read and write.

June 18, 2014838

Texas Instruments-Production Data

External Peripheral Interface (EPI)

Loading...

Loading...