Register 1: QSSI Control 0 (SSICR0), offset 0x000

The SSICR0 register contains bit fields that control various functions within the QSSI module.

Functionality such as protocol mode, clock rate, and data size are configured in this register.

QSSI Control 0 (SSICR0)

QSSI0 base: 0x4000.8000

QSSI1 base: 0x4000.9000

QSSI2 base: 0x4000.A000

QSSI3 base: 0x4000.B000

Offset 0x000

Type RW, reset 0x0000.0000

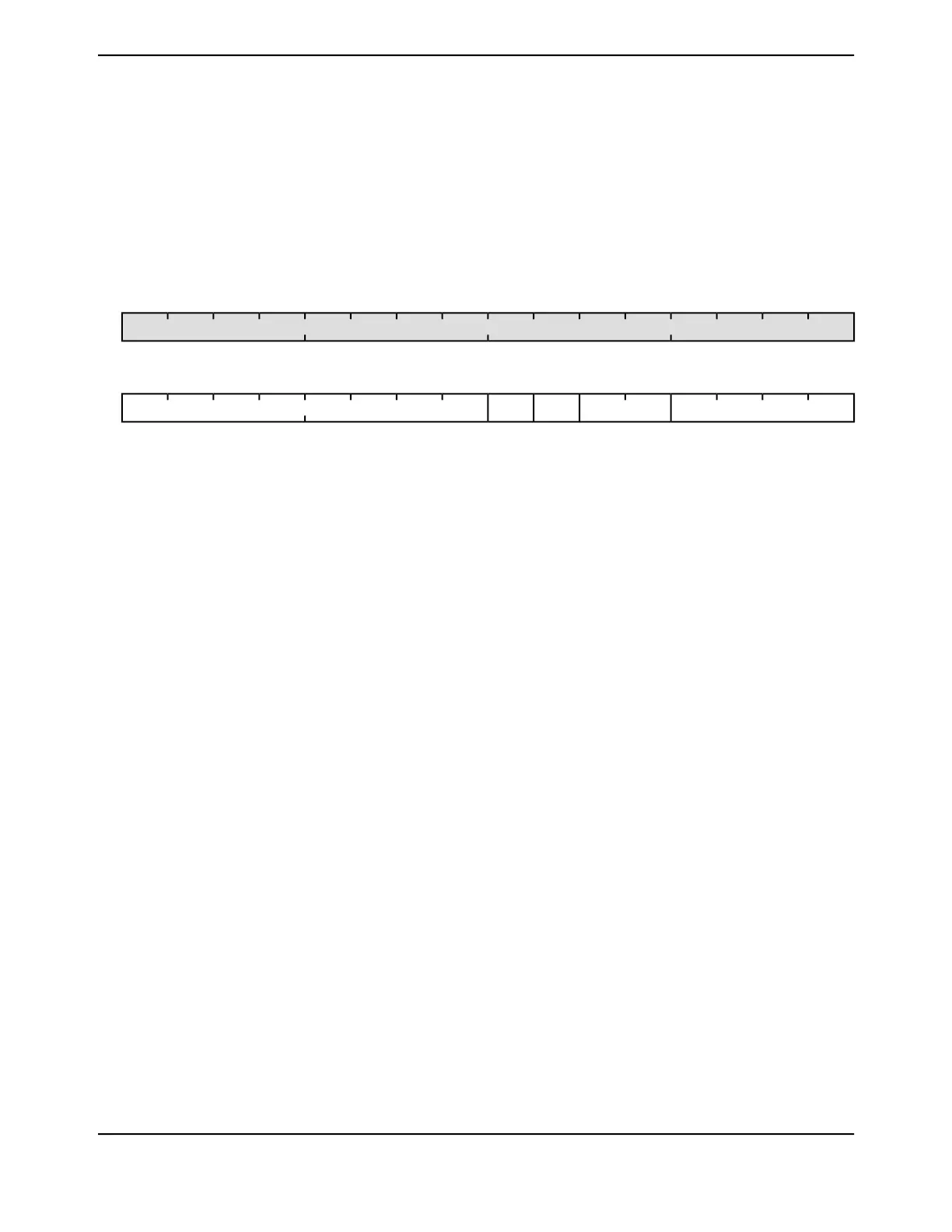

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

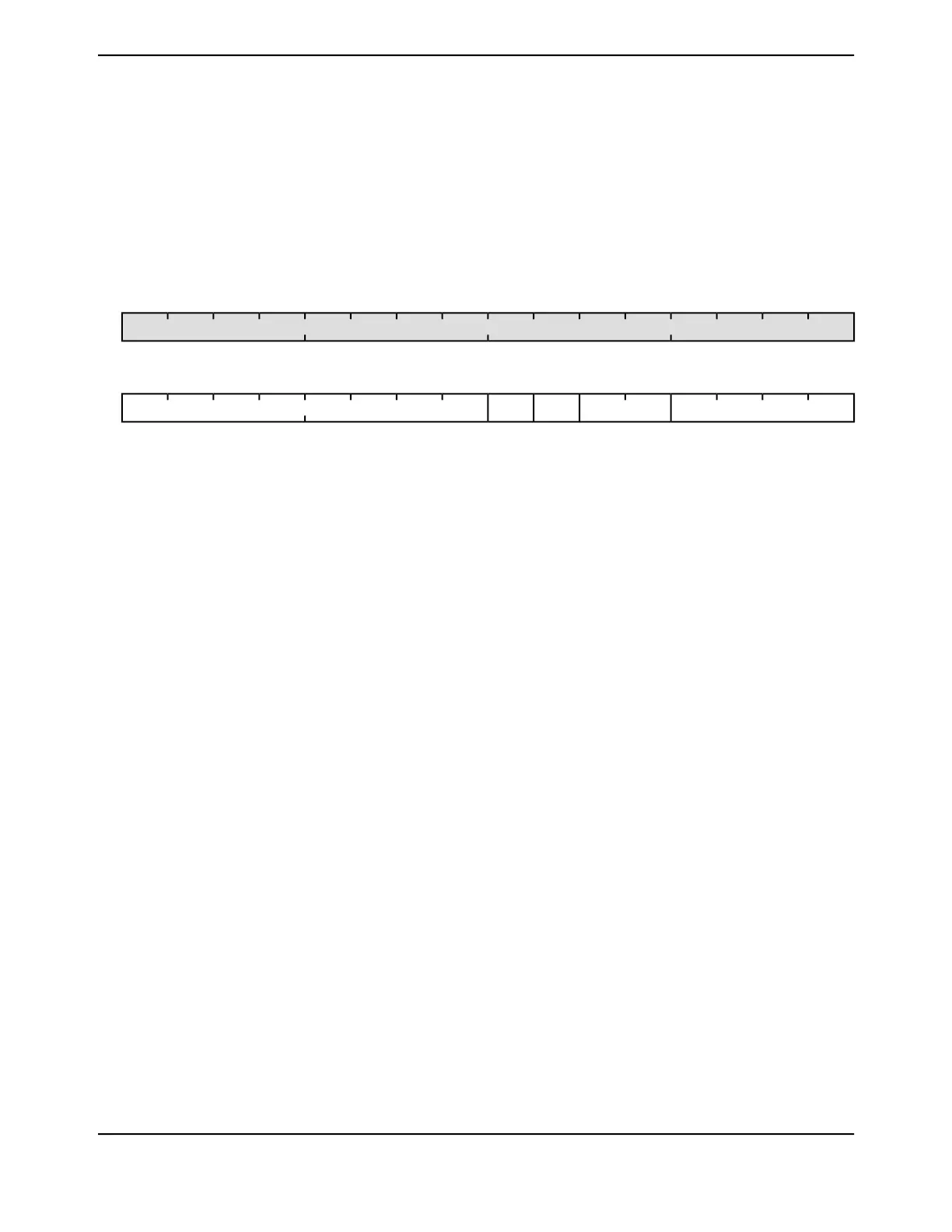

0123456789101112131415

DSSFRFSPOSPHSCR

RWRWRWRWRWRWRWRWRWRWRWRWRWRWRWRWType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000ROreserved31:16

QSSI Serial Clock Rate

This bit field is used to generate the transmit and receive bit rate of the

QSSI. The bit rate is:

BR=SysClk/(CPSDVSR * (1 + SCR))

where CPSDVSR is an even value from 2-254 programmed in the

SSICPSR register, and SCR is a value from 0-255.

0x00RWSCR15:8

QSSI Serial Clock Phase

This bit is only applicable to the Freescale SPI Format.

The SPH control bit selects the clock edge that captures data and allows

it to change state. This bit has the most impact on the first bit transmitted

by either allowing or not allowing a clock transition before the first data

capture edge.

DescriptionValue

Data is captured on the first clock edge transition.0

Data is captured on the second clock edge transition.1

0RWSPH7

QSSI Serial Clock Polarity

DescriptionValue

A steady state Low value is placed on the SSInClk pin.0

A steady state High value is placed on the SSInClk pin when

data is not being transferred.

1

Note: If this bit is set, then software must also configure the

GPIO port pin corresponding to the SSInClk signal

as a pull-up in the GPIO Pull-Up Select (GPIOPUR)

register.

0RWSPO6

1245June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...