Register 33: ADC Sample Sequence 1 Operation (ADCSSOP1), offset 0x070

Register 34: ADC Sample Sequence 2 Operation (ADCSSOP2), offset 0x090

This register determines whether the sample from the given conversion on Sample Sequence n is

saved in the Sample Sequence n FIFO or sent to the digital comparator unit. The ADCSSOP1

register controls Sample Sequencer 1 and the ADCSSOP2 register controls Sample Sequencer 2.

ADC Sample Sequence n Operation (ADCSSOPn)

ADC0 base: 0x4003.8000

ADC1 base: 0x4003.9000

Offset 0x070

Type RW, reset 0x0000.0000

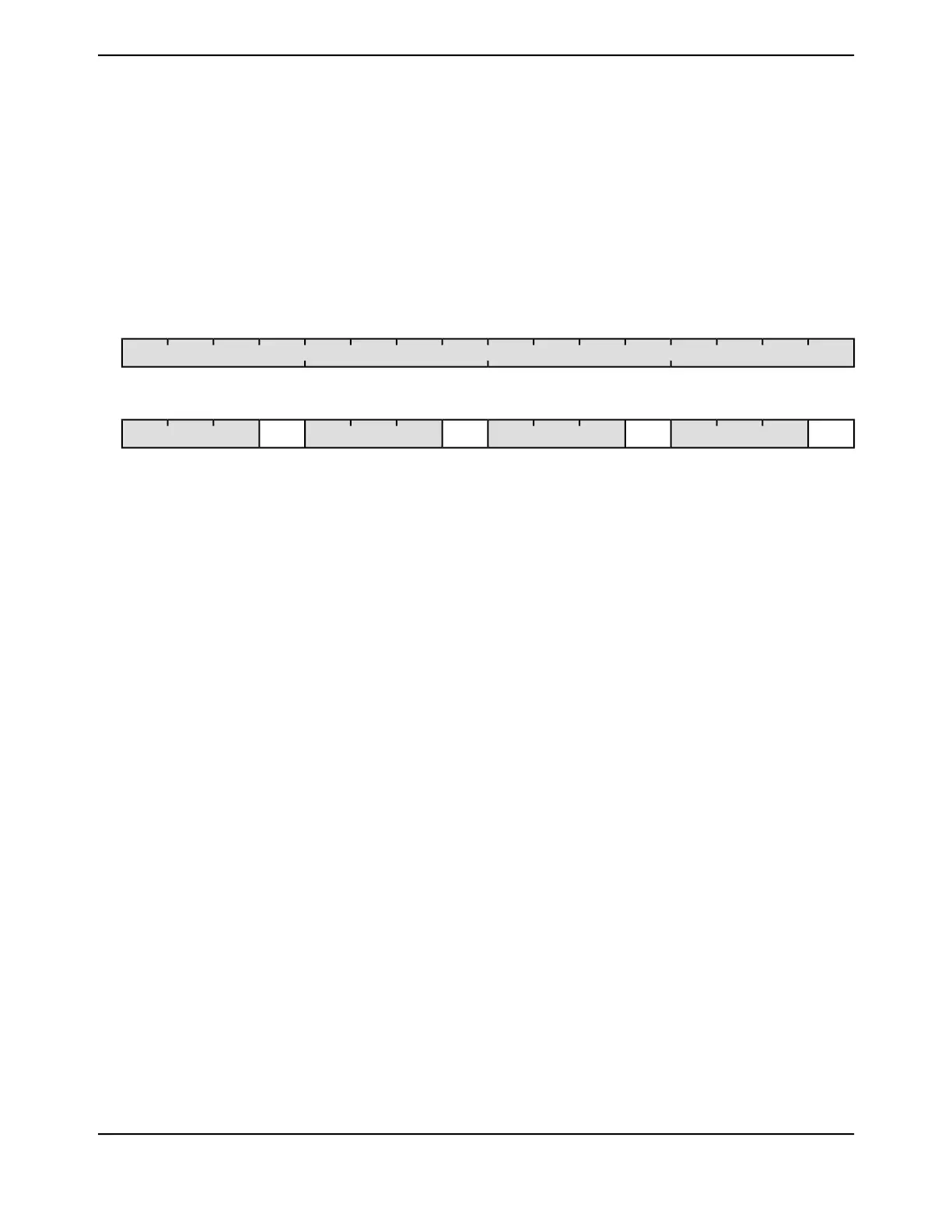

16171819202122232425262728293031

reserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

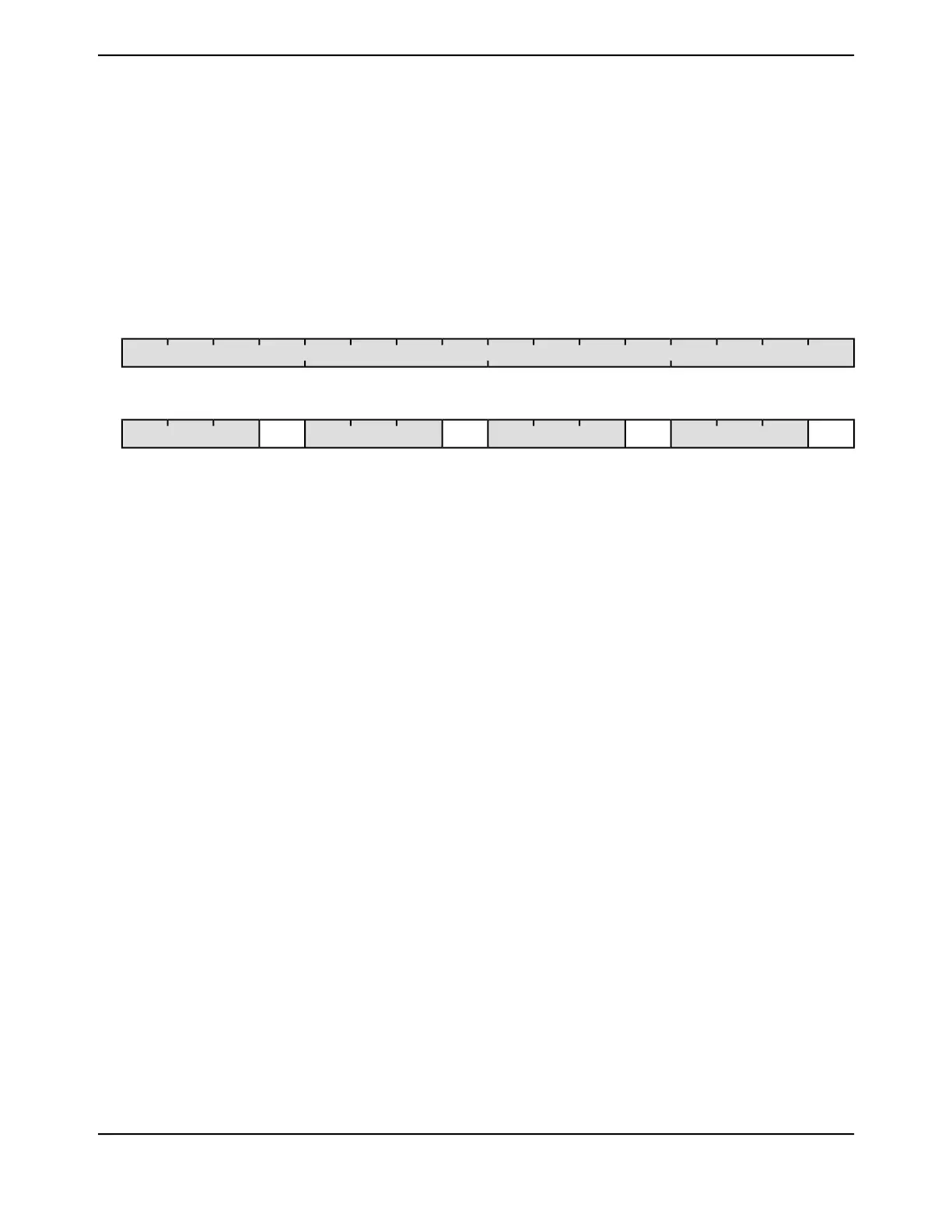

0123456789101112131415

S0DCOPreservedS1DCOPreservedS2DCOPreservedS3DCOPreserved

RWRORORORWRORORORWRORORORWROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.0ROreserved31:13

Sample 3 Digital Comparator Operation

DescriptionValue

The fourth sample is saved in Sample Sequence FIFOn.0

The fourth sample is sent to the digital comparator unit specified

by the S3DCSEL bit in the ADCSSDC0n register, and the value

is not written to the FIFO.

1

0RWS3DCOP12

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved11:9

Sample 2 Digital Comparator Operation

Same definition as S3DCOP but used during the third sample.

0RWS2DCOP8

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved7:5

Sample 1 Digital Comparator Operation

Same definition as S3DCOP but used during the second sample.

0RWS1DCOP4

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved3:1

Sample 0 Digital Comparator Operation

Same definition as S3DCOP but used during the first sample.

0RWS0DCOP0

June 18, 20141134

Texas Instruments-Production Data

Analog-to-Digital Converter (ADC)

Loading...

Loading...