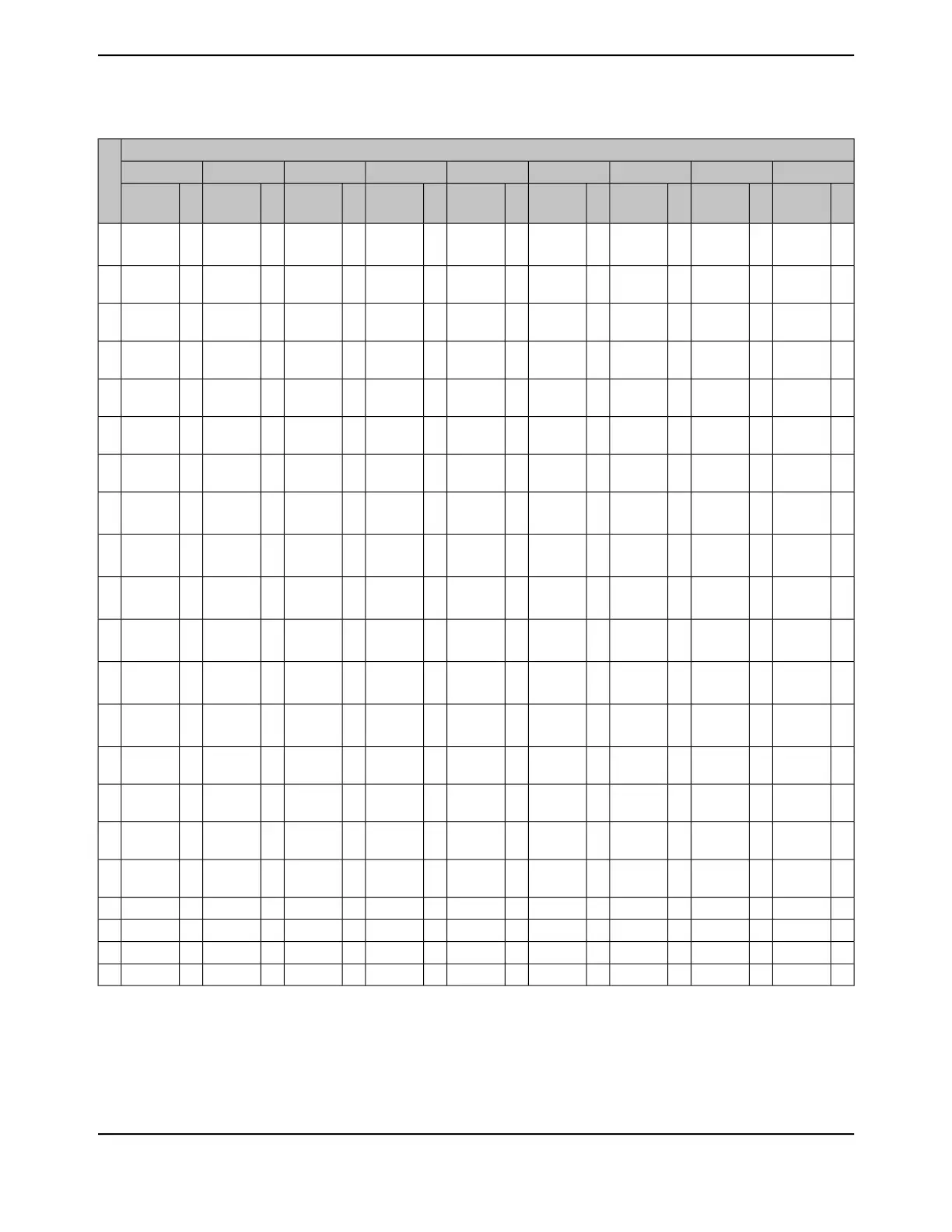

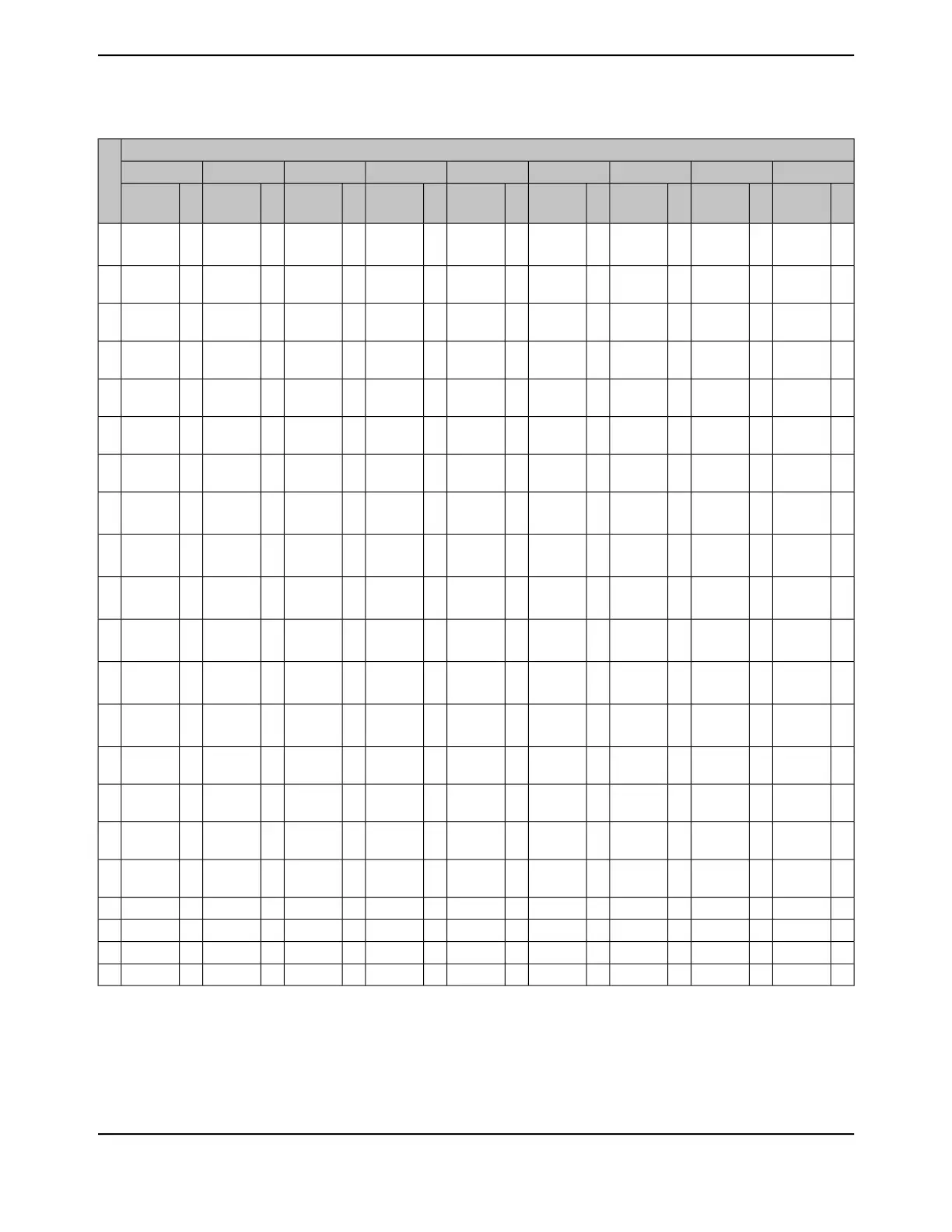

Table 9-1. μDMA Channel Assignments (continued)

Encoding

Channel

876543210

Type

Peripheral

Type

Peripheral

Type

Peripheral

Type

Peripheral

Type

Peripheral

Type

Peripheral

Type

Peripheral

Type

Peripheral

Type

Peripheral

-ReservedBGPTimer

6B

-Reserved-ReservedSB

B

I2C2 TX-ReservedSBUART6

TX

SBSSI1 TXSBSSI0 TX11

-ReservedBGPTimer

7A

-ReservedBSoftwareBGPIO K-ReservedSBSSI2 RXSBUART2

RX

-Reserved12

-ReservedBGPTimer

7B

-ReservedBSoftwareBGPIO L-ReservedSBSSI2 TXSBUART2

TX

-Reserved13

-Reserved-Reserved-ReservedBSoftwareBGPIO MBGPIO ESBSSI3 RXBGPTimer

2A

SBADC0

SS0

14

-Reserved-Reserved-ReservedBSoftwareBGPIO NBGPIO FSBSSI3 TXBGPTimer

2B

SBADC0

SS1

15

-Reserved-Reserved-Reserved-ReservedBGPIO P-ReservedSBUART3

RX

-ReservedSBADC0

SS2

16

-Reserved-Reserved-Reserved-Reserved-Reserved-ReservedSBUART3

TX

-ReservedSBADC0

SS3

17

-Reserved-Reserved-Reserved-ReservedSB

B

I2C3 RXBGPIO BSBUART4

RX

BGPTimer

1A

BGPTimer

0A

18

-Reserved-Reserved-Reserved-ReservedSB

B

I2C3 TXBGPIO GSBUART4

TX

BGPTimer

1B

BGPTimer

0B

19

-Reserved-Reserved-ReservedBSoftwareSB

B

I2C4 RXBGPIO HSBUART7

RX

BEPI 0 RX

Software

BGPTimer

1A

20

-Reserved-Reserved-ReservedBSoftwareSB

B

I2C4 TXBGPIO JSBUART7

TX

BEPI 0 TX

Software

BGPTimer

1B

21

BI2C8 RX-Reserved-ReservedBSoftwareSB

B

I2C5 RXBSoftware-ReservedBSoftwareSBUART1

RX

22

BI2C8 TX-Reserved-Reserved-ReservedSB

B

I2C5 TXBSoftware-ReservedBSoftwareSBUART1

TX

23

BI2C9 RX-Reserved-Reserved-ReservedBGPIO Q-Reserved-ReservedSBADC1

SS0

SBSSI1 RX24

BI2C9 TX-Reserved-Reserved-ReservedSoftware-Reserved-ReservedSBADC1

SS1

SBSSI1 TX25

BI2C6 RX-Reserved-Reserved-ReservedSoftware-Reserved-ReservedSBADC1

SS2

BSoftware26

BI2C6 TX-ReservedBSoftware-Reserved-Reserved-Reserved-ReservedSBADC1

SS3

BSoftware27

BI2C7 RX-Reserved-Reserved-Reserved-Reserved-Reserved-Reserved-Reserved-Reserved28

BI2C7 TX-Reserved-Reserved-Reserved-Reserved-Reserved-Reserved-Reserved-Reserved29

BSoftwareBEPI0 RX-Reserved-Reserved-ReservedBSoftware-ReservedBSoftwareBSoftware30

-ReservedBEPI0 TX-Reserved-Reserved-ReservedBReserved-Reserved-Reserved-Reserved31

9.2.2 Priority

The μDMA controller assigns priority to each channel based on the channel number and the priority

level bit for the channel. Channel number 0 has the highest priority and as the channel number

increases, the priority of a channel decreases. Each channel has a priority level bit to provide two

681June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...