Register 1: SysTick Control and Status Register (STCTRL), offset 0x010

Note: This register can only be accessed from privileged mode.

The SysTick STCTRL register enables the SysTick features.

SysTick Control and Status Register (STCTRL)

Base 0xE000.E000

Offset 0x010

Type RW, reset 0x0000.0000

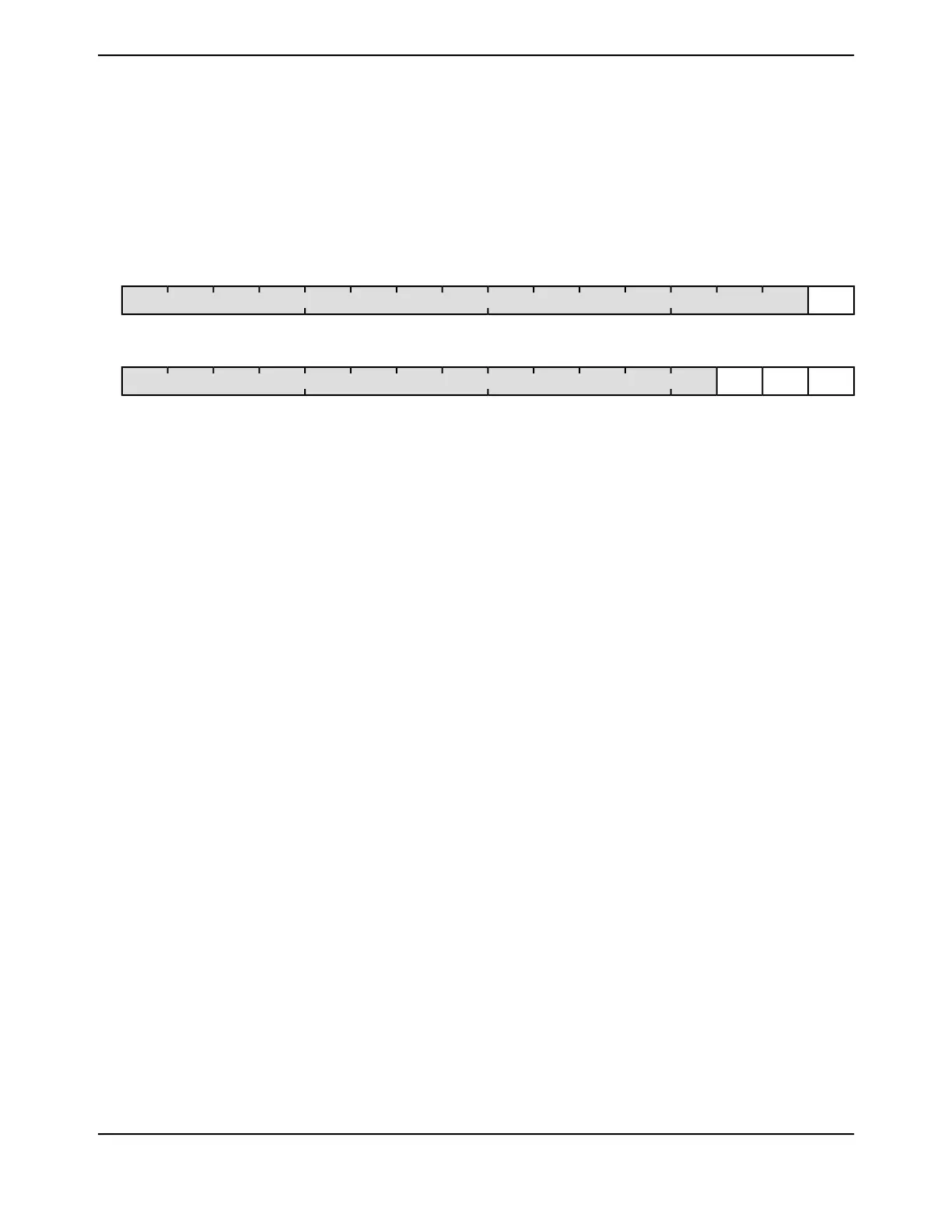

16171819202122232425262728293031

COUNTreserved

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

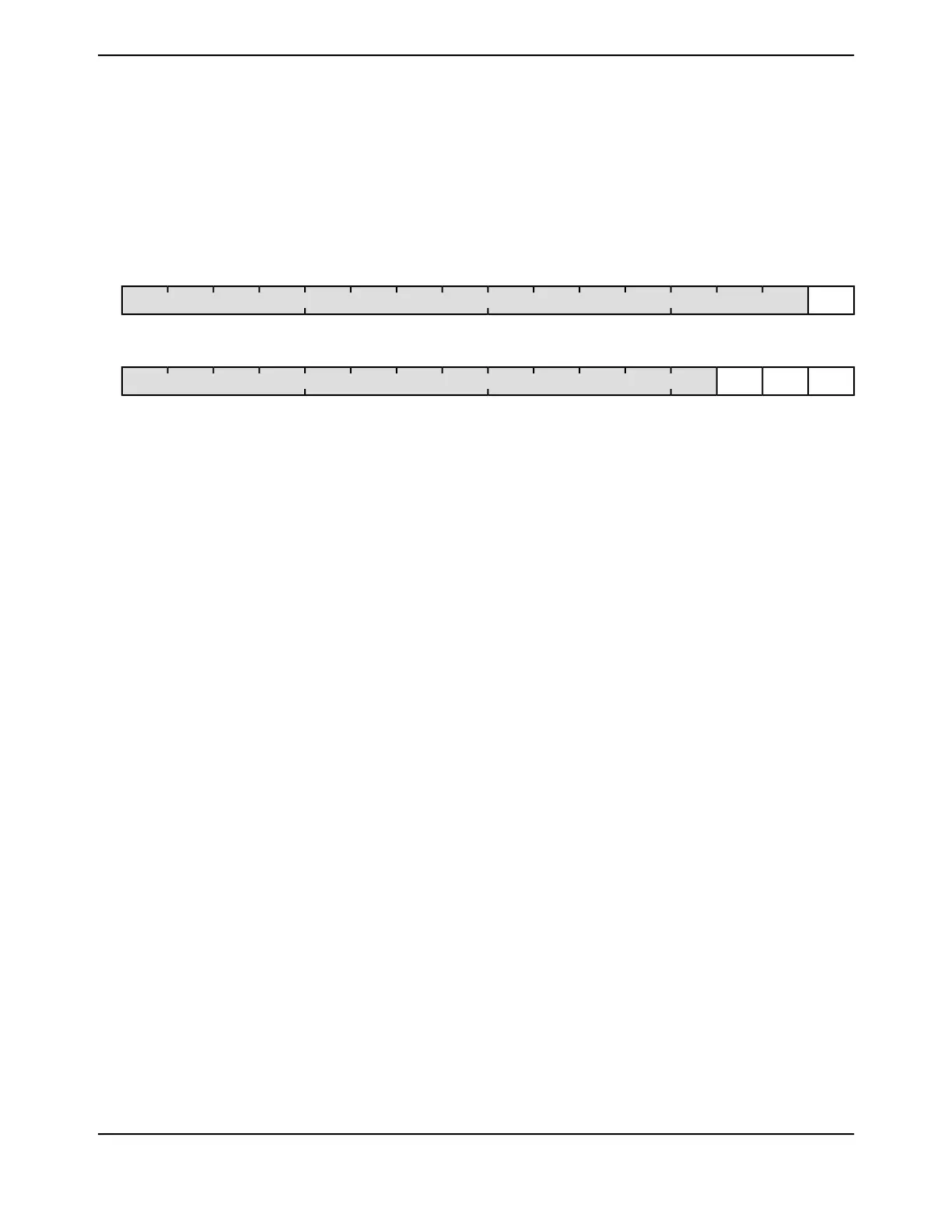

0123456789101112131415

ENABLEINTENCLK_SRCreserved

RWRWRWROROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x000ROreserved31:17

Count Flag

DescriptionValue

The SysTick timer has not counted to 0 since the last time

this bit was read.

0

The SysTick timer has counted to 0 since the last time

this bit was read.

1

This bit is cleared by a read of the register or if the STCURRENT register

is written with any value.

If read by the debugger using the DAP, this bit is cleared only if the

MasterType bit in the AHB-AP Control Register is clear. Otherwise,

the COUNT bit is not changed by the debugger read. See the ARM®

Debug Interface V5 Architecture Specification for more information on

MasterType.

0ROCOUNT16

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x000ROreserved15:3

Clock Source

DescriptionValue

Precision internal oscillator (PIOSC) divided by 40

System clock1

0RWCLK_SRC2

June 18, 2014150

Texas Instruments-Production Data

Cortex-M4 Peripherals

Loading...

Loading...