Register 11: Hibernation IO Configuration (HIBIO), offset 0x02C

This register is used to lock and unlock the external wake pin levels and enable the external RST

pin and/or GPIO pins, Port K[7:4], as valid external WAKE sources.

Note: This register is in the system clock domain and does not require monitoring the WRC bit of

the HIBCTL register before issuing a read or write of this register. Writes to this register are

immediate.

Note: This register is in the core voltage domain and will not retain values over a hibernate cycle

Hibernation IO Configuration (HIBIO)

Base 0x400F.C000

Offset 0x02C

Type RW, reset 0x8000.0000

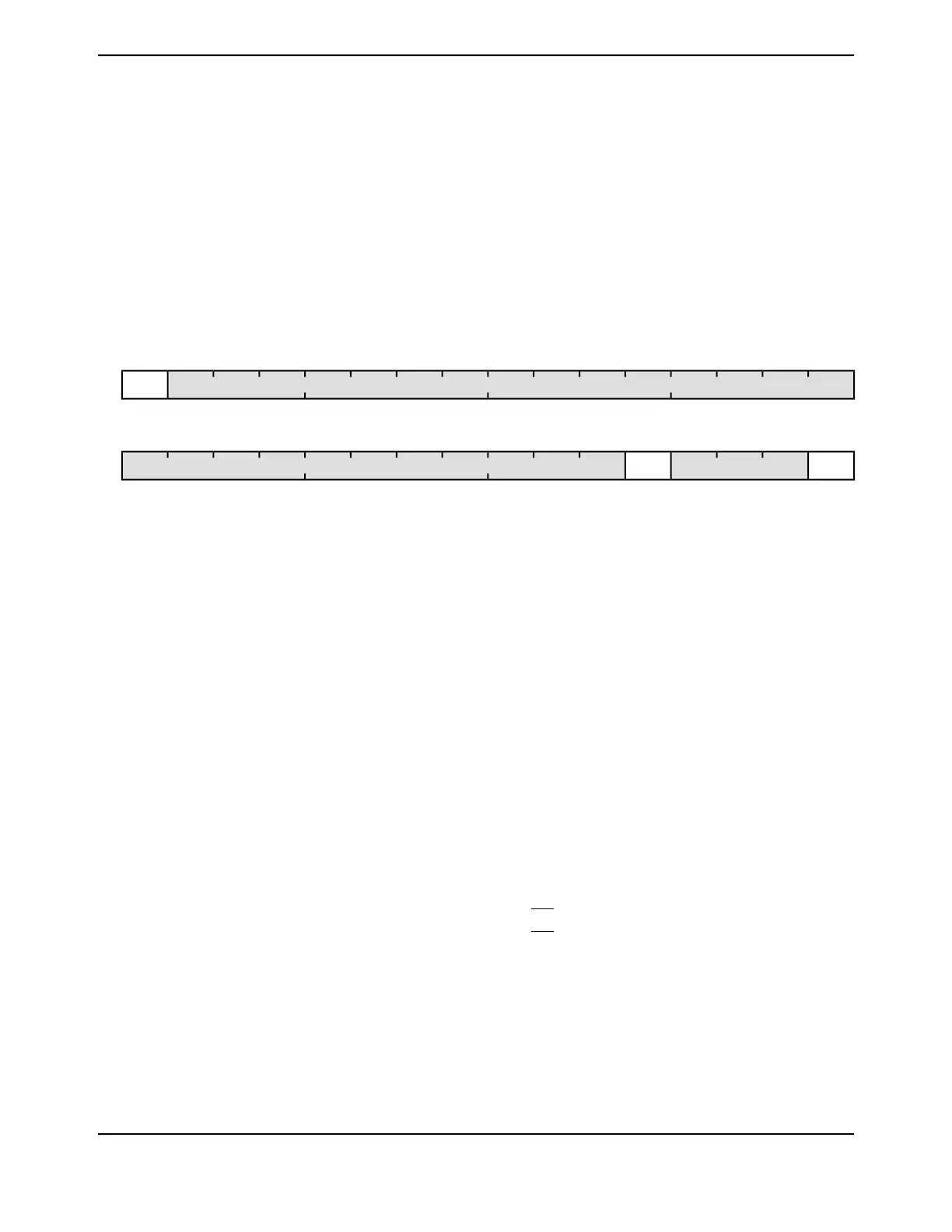

16171819202122232425262728293031

reservedIOWRC

ROROROROROROROROROROROROROROROROType

0000000000000001Reset

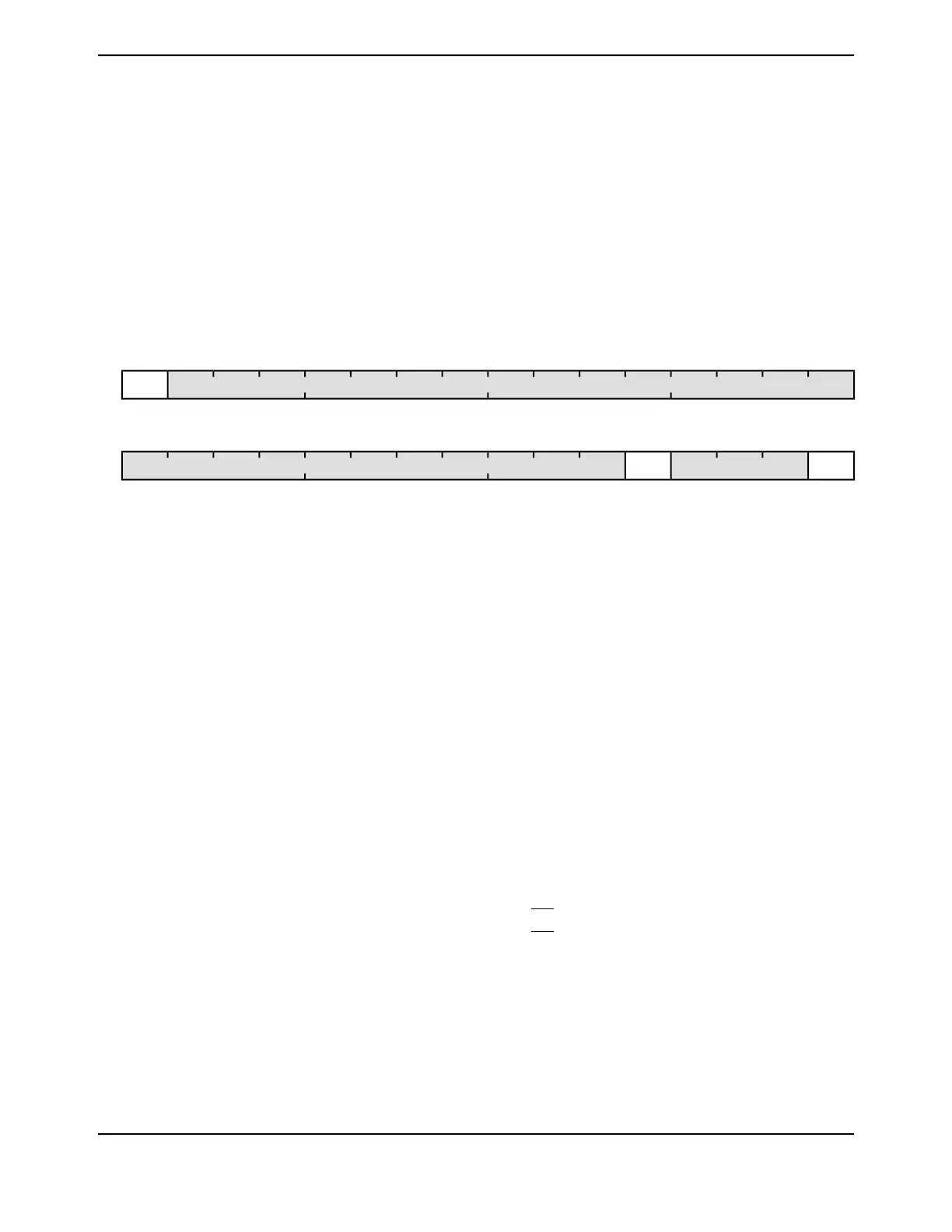

0123456789101112131415

WUUNLKreservedWURSTENreserved

RWRORORORWROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

I/O Write Complete

Indicates whether or not the configuration that was programmed by the

WURSTEN bit or GPIOWAKEPEN and GPIOWAKELVL registers have

propagated through the pad ring.

DescriptionValue

The changes programmed in the external pad I/O wake source

registers have not propagated through the pad I/O.

0

The changes programmed in the external pad I/O wake source

registers have propagated through the pad I/O.

1

0x1ROIOWRC31

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0000.000ROreserved30:5

Reset Wake Source Enable

This register bit programming takes affect after WUUNLK has been set.

DescriptionValue

The RST signal is not enabled as a wake source.0

The RST signal is enabled as a wake source.1

0RWWURSTEN4

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved3:1

June 18, 2014572

Texas Instruments-Production Data

Hibernation Module

Loading...

Loading...