Register 56: Interrupt Control and State (INTCTRL), offset 0xD04

Note: This register can only be accessed from privileged mode.

The INCTRL register provides a set-pending bit for the NMI exception, and set-pending and

clear-pending bits for the PendSV and SysTick exceptions. In addition, bits in this register indicate

the exception number of the exception being processed, whether there are preempted active

exceptions, the exception number of the highest priority pending exception, and whether any interrupts

are pending.

When writing to INCTRL, the effect is unpredictable when writing a 1 to both the PENDSV and

UNPENDSV bits, or writing a 1 to both the PENDSTSET and PENDSTCLR bits.

Interrupt Control and State (INTCTRL)

Base 0xE000.E000

Offset 0xD04

Type RW, reset 0x0000.0000

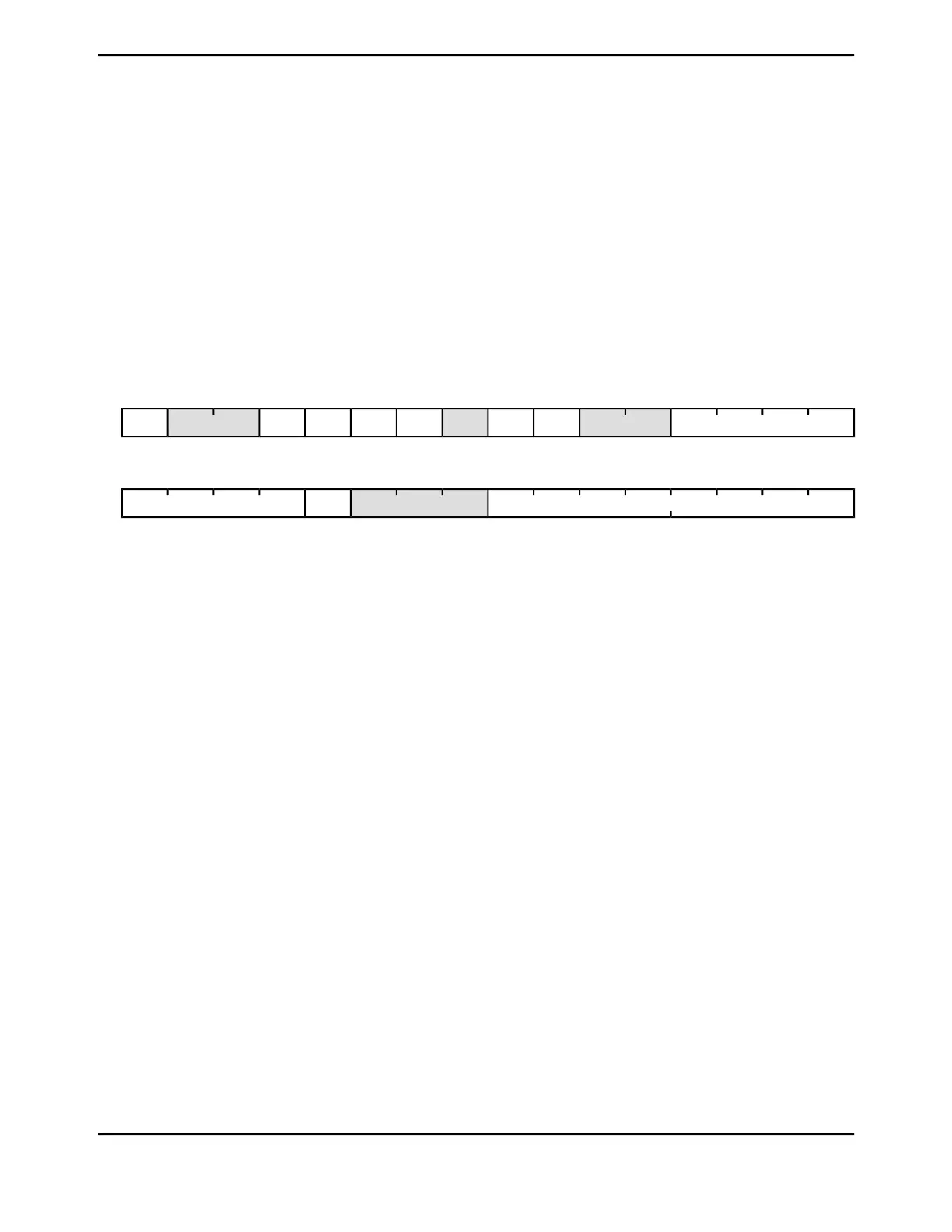

16171819202122232425262728293031

VECPENDreservedISRPENDISRPREreserved

PENDSTCLRPENDSTSET

UNPENDSV

PENDSVreservedNMISET

ROROROROROROROROROWORWWORWRORORWType

0000000000000000Reset

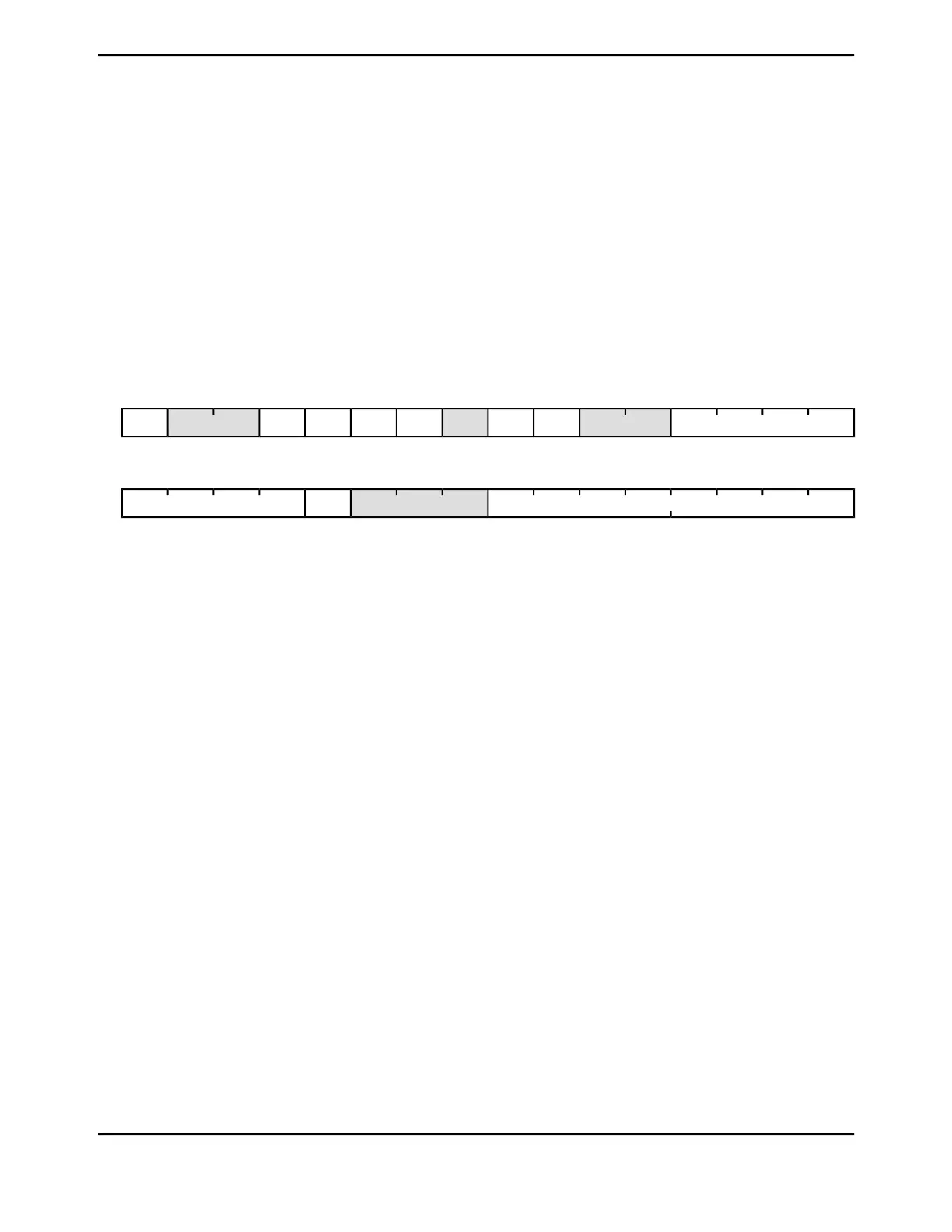

0123456789101112131415

VECACTreservedRETBASEVECPEND

ROROROROROROROROROROROROROROROROType

0000000000000000Reset

DescriptionResetTypeNameBit/Field

NMI Set Pending

DescriptionValue

On a read, indicates an NMI exception is not pending.

On a write, no effect.

0

On a read, indicates an NMI exception is pending.

On a write, changes the NMI exception state to pending.

1

Because NMI is the highest-priority exception, normally the processor

enters the NMI exception handler as soon as it registers the setting of

this bit, and clears this bit on entering the interrupt handler. A read of

this bit by the NMI exception handler returns 1 only if the NMI signal is

reasserted while the processor is executing that handler.

0RWNMISET31

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0x0ROreserved30:29

PendSV Set Pending

DescriptionValue

On a read, indicates a PendSV exception is not pending.

On a write, no effect.

0

On a read, indicates a PendSV exception is pending.

On a write, changes the PendSV exception state to pending.

1

Setting this bit is the only way to set the PendSV exception state to

pending. This bit is cleared by writing a 1 to the UNPENDSV bit.

0RWPENDSV28

167June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...