Descriptor List Address (EMACTXDLADDR) register providing the DMA with the starting

address of each list.

4. Write to the Ethernet MAC Frame Filter (EMACFRAMEFLTR) register, the Ethernet MAC

Hash Table High (EMACHASHTBLH) and the Ethernet MAC Hash Table Low

(EMACHASHTBLL) for desired filtering options.

5. Write to the Ethernet MAC Configuration Register (EMACCFG) to configure the operating

mode and enable the transmit operation.

6. Program Bit 15 (PS) and Bit 11 (DM) of the EMACCFG register based on the line status received

or read from the PHY status register after auto-negotiation.

7. Write to the Ethernet MAC DMA Operation Mode (EMACDMAOPMODE) register to set Bits

13 and 1 to start transmission and reception.

8. Write to the EMACCFG register to enable the receive operation.

The Transmit and Receive engines enter the Running state and attempt to acquire descriptors

from the respective descriptor lists. The Receive and Transmit engines then begin processing

Receive and Transmit operations. The Transmit and Receive processes are independent of

each other and can be started or stopped separately.

20.5.1 Ethernet PHY Initialization

After reset, when the EMAC is powered and enabled, the EMACPC register default reset value may

be sampled and used to configure the PHY. The results of this configuration can also be read in the

following EPHY registers:

■ EPHYBMCR register (MR0)

■ EPHYCFG1 register (MR9)

■ EPHYCFG2 register (MR10)

■ EPHYCFG3 register (MR11)

■ EPHYCTL register (MR25)

The mappings of the EMACPC register bits to the PHY register and bits are as follows:

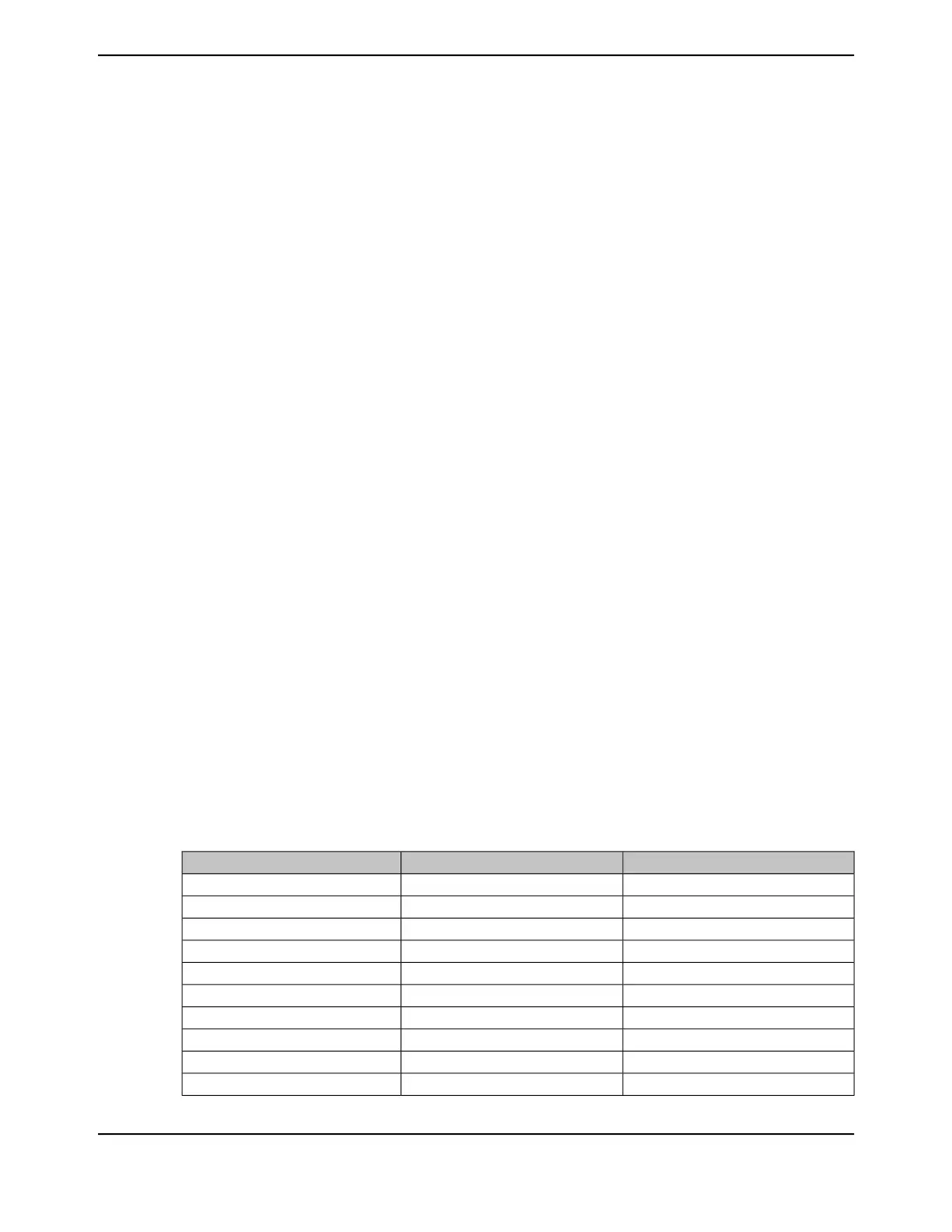

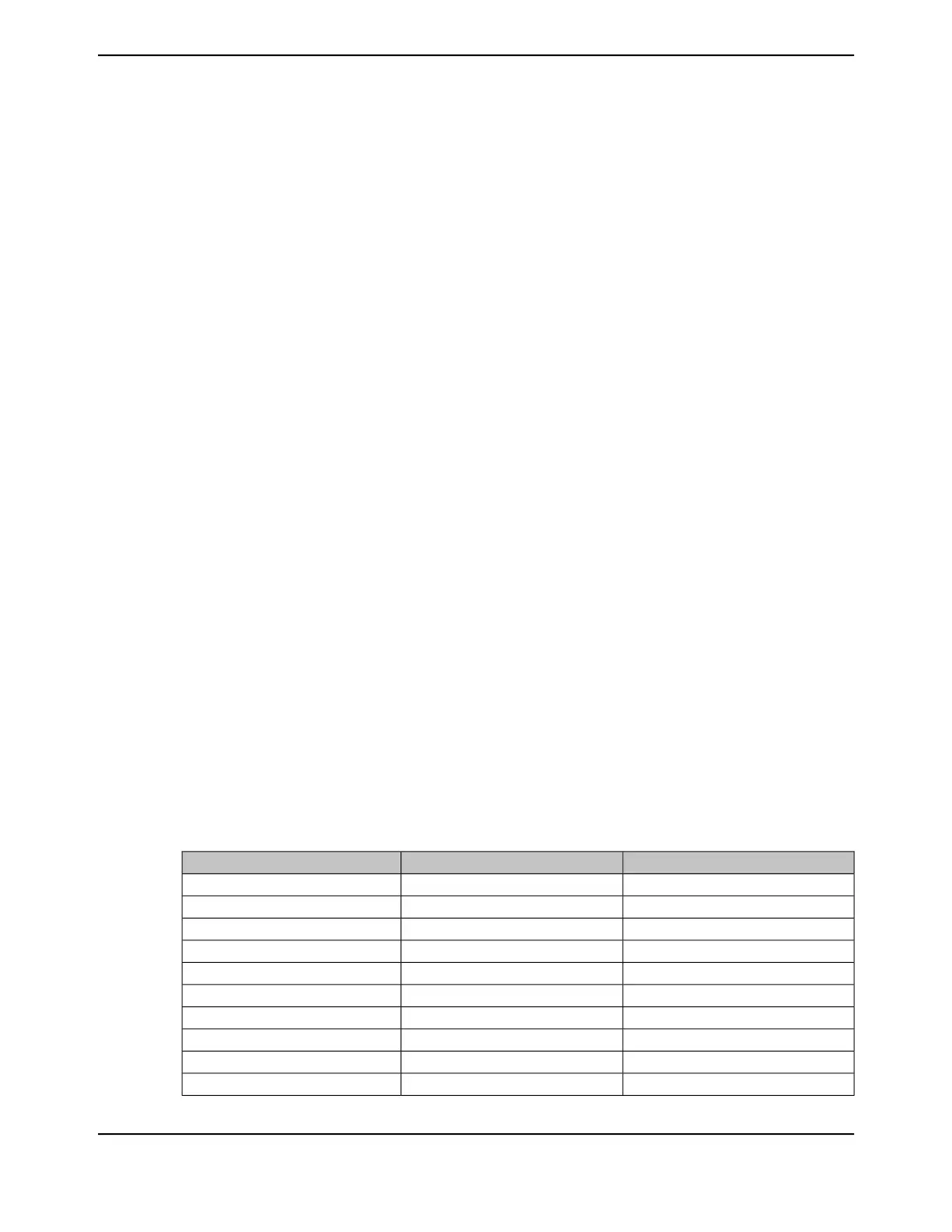

Table 20-22. EMACPC to PHY Register Mapping

Corresponding PHY Bit (Bit No.)Corresponding PHY RegisterEMACPC Register Bit

N/AN/APHYEXT

N/AN/ADIGRESTART

ODDNDETDIS (1)EPHYCFG2NIBDETDIS

RXERRIDLE (2)EPHYCFG2RXERIDLE

ISOMILL (3)EPHYCFG2ISOMILL

LLR (7)EPHYCFG1LRR

TDRAR (8)EPHYCFG1TDRRUN

FLDWNM (4:0)EPHYCFG3FASTLDMODE

POLSWAP (7)EPHYCFG3POLSWAP

MDIMDIXS (6)EPHYCFG3MDISWAP

1465June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller

Loading...

Loading...