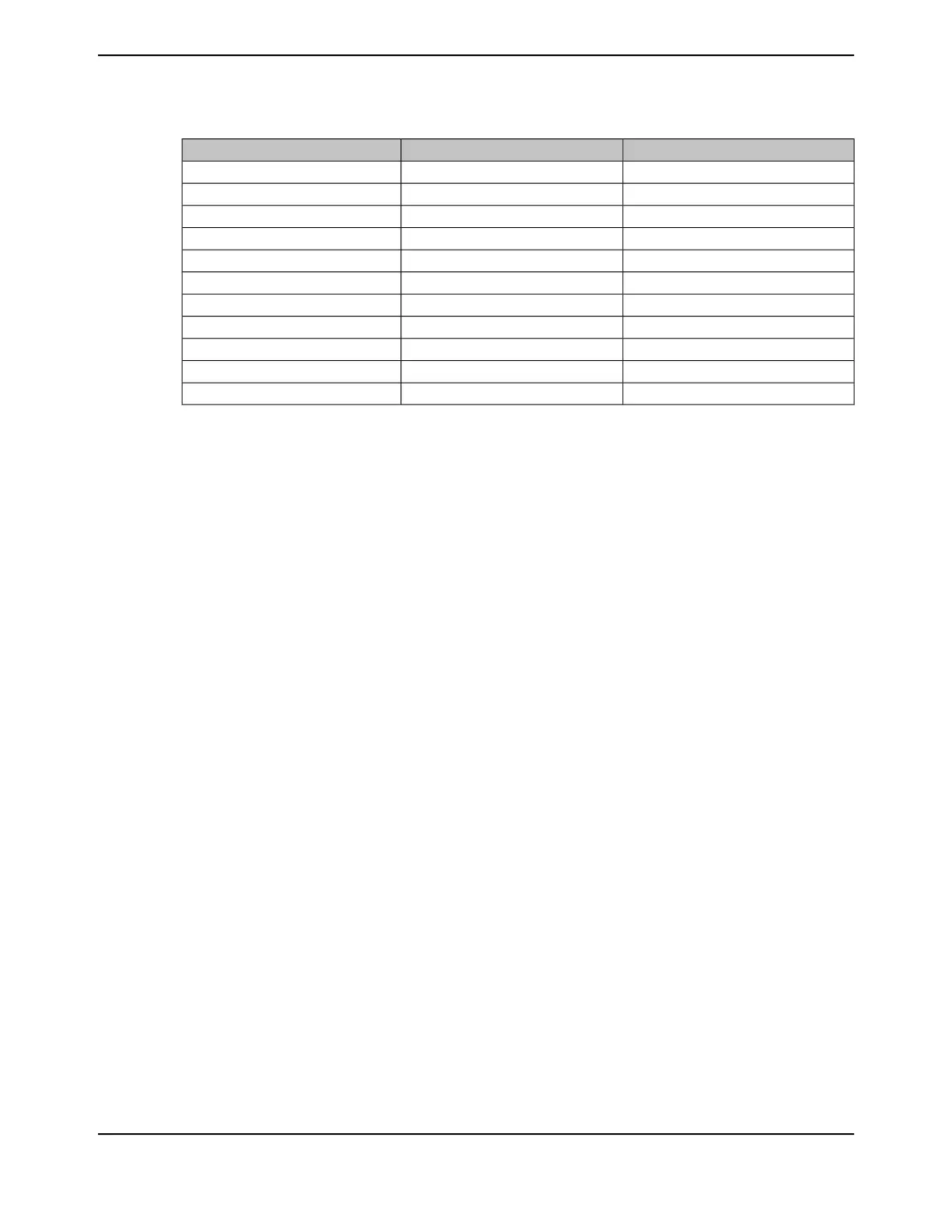

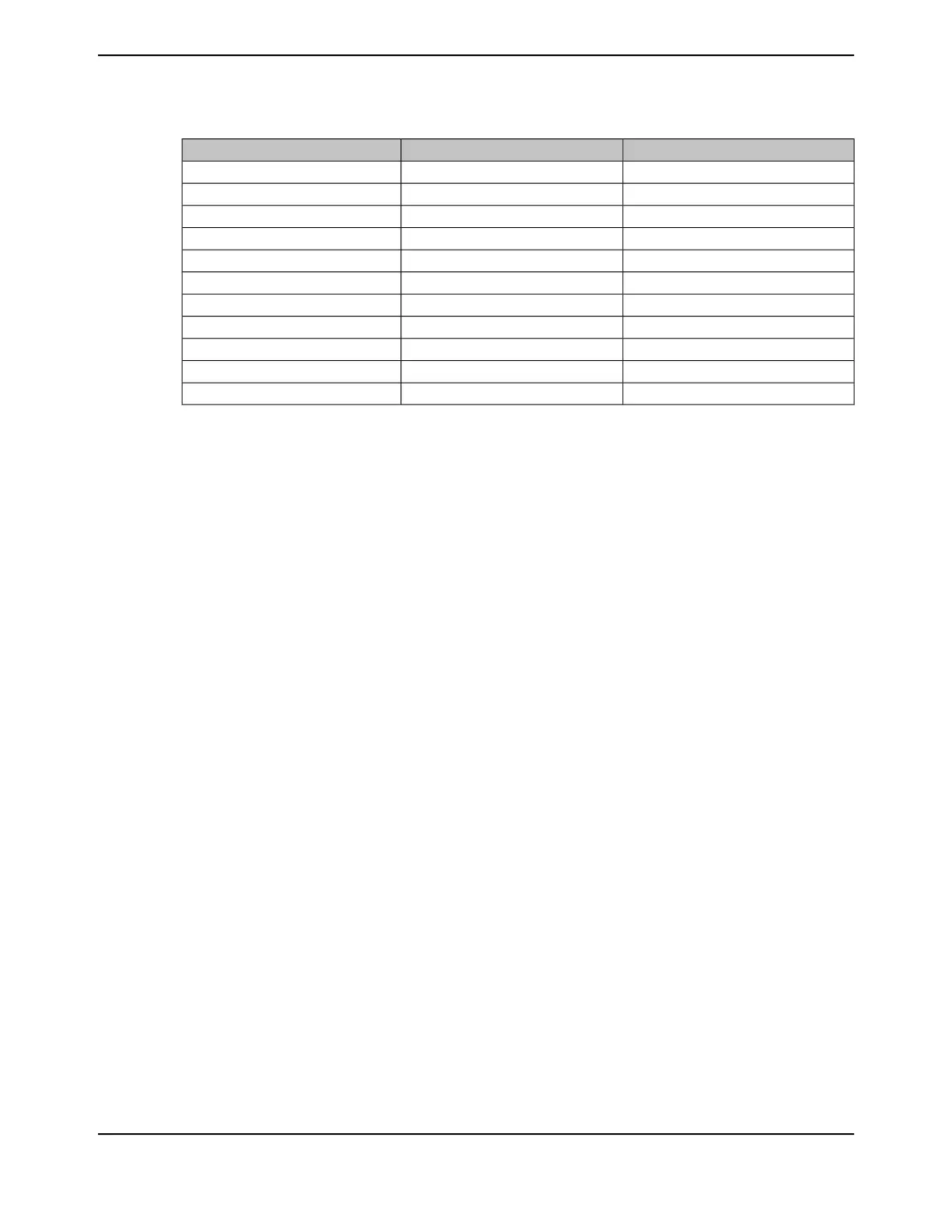

Table 20-22. EMACPC to PHY Register Mapping (continued)

Corresponding PHY Bit (Bit No.)Corresponding PHY RegisterEMACPC Register Bit

RAMDIX (5)EPHYCFG1RBSTMDIX

FAMDIX (6)EPHYCFG1FASTMDIX

AUTOMDI (15)EPHYCTLMDIXEN

FRXDVDET (1)EPHYCFG1FASTRXDV

FLUPPD (6)EPHYCFG2FASTLUPD

EXTFD (5)EPHYCFG2EXTFD

FASTANEN (4)EPHYCFG1FASTANEN

FANSEL (3:2)EPHYCFG1FASTANSEL

ANENEPHYBMCRANEN

N/AN/AANMODE

N/AN/APHYHOLD

The MAC module and registers are enabled and powered at reset. When reset has completed and

the clock to the Ethernet MAC is enabled by setting the R0 bit in the Ethernet Controller Run Mode

Clock Gating Control (RCGCEMAC) register at System Control Module offset 0x69C, the application

has the option to enable the PHY with its default interface configuration (as defined by the Ethernet

MAC Peripheral Configuration Register (EMACPC) register) or with a custom configuration.

20.5.1.1 Default Configuration

To enable the Ethernet PHY with its default configuration, the steps are as follows:

1. To hold the Ethernet PHY from transmitting energy on the line during configuration, set the

PHYHOLD bit to 1 in the EMACPC register.

2. Enable the clock to the PHY module by writing 0x0000.0001 to the Ethernet PHY Run Mode

Clock Gating Control (RCGCEPHY) register at offset 0x630. When the R0 bit reads as 1 in

the PREPHY register at System Control offset 0xA30, continue initialization.

3. Enable power to the Ethernet PHY by setting the P0 bit in the PCEPHY register at System

Control offset 0x930. When the R0 bit reads as 1 in the PREPHY register at System Control

offset 0xA30, the PHY registers are ready for programming.

20.5.1.2 Custom Configuration

If a custom configuration of the Ethernet PHY is required, the application can program the

configuration registers after reset. The steps for custom configuration are as follows:

1. To hold the PHY from transmitting energy on the line during configuration, set the PHYHOLD bit

to 1 in the EMACPC register.

2. Enable the clock to the PHY module by writing 0x0000.0001 to the Ethernet PHY Run Mode

Clock Gating Control (RCGCEPHY) register at offset 0x630. When the R0 bit reads as 1 in

the PREPHY register at System Control offset 0xA30, continue initialization.

3. Enable power to the Ethernet PHY by setting the P0 bit in the PCEPHY register at System

Control offset 0x930. When the R0 bit reads as 1 in the PREPHY register at System Control

offset 0xA30, the PHY registers are ready for programming.

June 18, 20141466

Texas Instruments-Production Data

Ethernet Controller

Loading...

Loading...